# UM1922 User manual

# VIPower® M0-7 standard high-side drivers hardware design guide

#### Introduction

VIPower<sup>®</sup> parallel high-side drivers have reached the 7<sup>th</sup> generation of smart power drivers (internally called M0-7). In this latest set of drivers all the experience and know-how from existing features of the previous generations as well as new features have been implemented.

The continuous increasing demanding requirements from automotive customers in terms of quality, reliability, flexibility and cost effective system solutions represent the basic factor of new protection feature concept (latch off in overload condition beside the already known auto restart feature) and new diagnostic features like real time device case temperature and battery terminal voltage sensing beside the already existing output current sensing available to the microcontroller in a unique "MultiSense" pin.

Purpose of this user manual is to give a comprehensive "tool kit" for a better understanding of the behavior of the M0-7 parallel High Side Drivers (abbreviation HSDs) in their application usage context and thus allowing the design engineer an easier design in.

July 2015 DocID028098 Rev 1 1/196

Contents UM1922

# **Contents**

| 1 | Gen  | al items                                                                                 |  |  |  |  |

|---|------|------------------------------------------------------------------------------------------|--|--|--|--|

|   | 1.1  | Overview about M0-7 standard high-side drivers                                           |  |  |  |  |

|   | 1.2  | Application schematics – monolithic devices                                              |  |  |  |  |

|   | 1.3  | Application schematics – hybrid devices                                                  |  |  |  |  |

|   | 1.4  | Application schematics – description of external components                              |  |  |  |  |

| 2 | Rev  | se battery protection                                                                    |  |  |  |  |

|   | 2.1  | Introduction                                                                             |  |  |  |  |

|   | 2.2  | Reverse battery protection of monolithic HSDs 1                                          |  |  |  |  |

|   |      | 2.2.1 Schottky diode                                                                     |  |  |  |  |

|   |      | 2.2.2 Diode + resistor in GND line                                                       |  |  |  |  |

|   |      | 2.2.3 N-channel MOSFET in GND line                                                       |  |  |  |  |

|   |      | 2.2.4 P-channel MOSFET in the V <sub>CC</sub> line                                       |  |  |  |  |

|   |      | 2.2.5 Dedicated ST Reverse FET solution                                                  |  |  |  |  |

| 3 | Prot | ction against battery transients                                                         |  |  |  |  |

|   | 3.1  | Introduction on automotive electrical hazards                                            |  |  |  |  |

|   | 3.2  | Source of hazard on automotive 3                                                         |  |  |  |  |

|   |      | 3.2.1 Conducted hazards                                                                  |  |  |  |  |

|   | 3.3  | Propagation of electrical hazards on the supply rail                                     |  |  |  |  |

|   | 3.4  | Standard for the protection of automotive electronics                                    |  |  |  |  |

|   | 3.5  | Basic application schematic to protect a M0-7 standard monolithic high-siddriver         |  |  |  |  |

|   |      | 3.5.1 Components dimensioning                                                            |  |  |  |  |

|   | 3.6  | Component dimensioning for hybrid devices                                                |  |  |  |  |

|   |      | 3.6.1 Dimensioning of the series resistors on I/O line4                                  |  |  |  |  |

|   |      | 3.6.2 Dimensioning of the GND network to pass the ISO n.1 and 2a level IV (2011 edition) |  |  |  |  |

| 4 | Usa  | e/handling of fault reset and standby4                                                   |  |  |  |  |

|   | 4.1  | Latch-off functionality                                                                  |  |  |  |  |

|   | 4.2  | Standby mode 5                                                                           |  |  |  |  |

|   | 4.3  | Flexible blanking time (fault reset management) 5                                        |  |  |  |  |

UM1922 Contents

| 5 | Usag | ge and handling of MultiSense SEL pin                                    | 57    |

|---|------|--------------------------------------------------------------------------|-------|

|   | 5.1  | Classification of M0-7 HSDs                                              | 57    |

|   | 5.2  | SEL pins truth table (device dependant)                                  | 58    |

|   | 5.3  | Connection of SEL pins with control logic (Microcontroller)              | 59    |

| 6 | Load | d compatibility                                                          | 65    |

|   | 6.1  | Bulbs                                                                    | 65    |

|   | 6.2  | Power loss calculations                                                  | 69    |

|   |      | 6.2.1 Conduction losses                                                  | 70    |

|   |      | 6.2.2 Switching losses                                                   | 73    |

|   | 6.3  | Inductive loads                                                          | 95    |

|   |      | 6.3.1 Turn-on                                                            | 95    |

|   |      | 6.3.2 Turn-off                                                           | 96    |

|   |      | 6.3.3 Calculation of dissipated energy                                   | 97    |

|   |      | 6.3.4 Selection criterion with reference to I-L plot                     | 99    |

|   |      | 6.3.5 External clamping protection                                       | 102   |

|   |      | 6.3.6 Loss of V <sub>CC</sub>                                            | 109   |

| 7 | Mult | tiSense - analogue current sense                                         | . 117 |

|   | 7.1  | Introduction                                                             | 117   |

|   | 7.2  | Principle of MultiSense signal generation                                | 118   |

|   |      | 7.2.1 Current monitor                                                    | 119   |

|   |      | 7.2.2 Normal operation (channel ON, no fault, SE <sub>n</sub> active)    | 119   |

|   |      | 7.2.3 Current monitoring range of linear operation                       | 119   |

|   |      | 7.2.4 Impact of the output voltage to the MultiSense output              | 122   |

|   |      | 7.2.5 Failure flag indication                                            | 122   |

|   |      | 7.2.6 Considerations on MultiSense resistor choice for current monitor . | 124   |

|   |      | 7.2.7 Usage when multiplexing several devices                            | 127   |

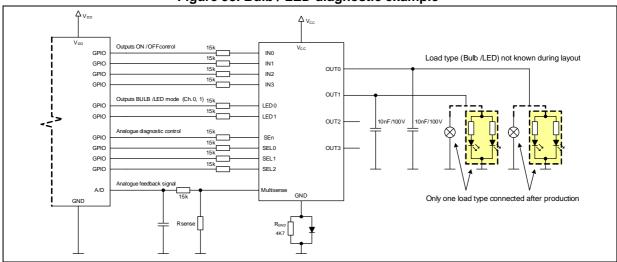

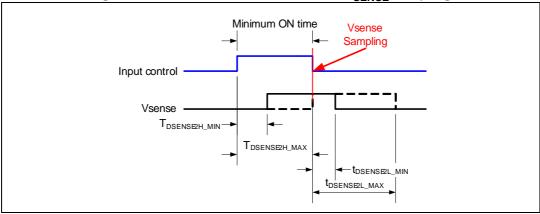

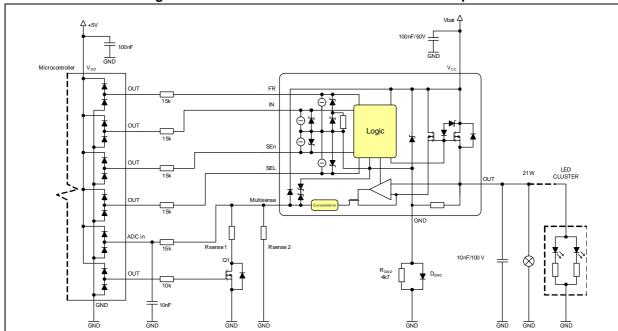

|   |      | 7.2.8 LED diagnostic                                                     | 127   |

|   |      | 7.2.9 Diagnostic with paralleled loads / partial load detection          | 130   |

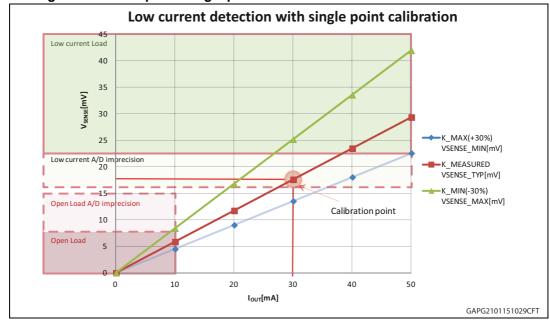

|   |      | 7.2.10 K factor calibration method                                       | 131   |

|   |      | 7.2.11 Open load detection in off-state                                  | 135   |

|   |      | 7.2.12 MultiSense diagnostic evaluation with SPC560Bxx                   | 142   |

|   |      | 7.2.13 MultiSense low pass filtering                                     | 148   |

|   | 7.3  | T <sub>CASE</sub> , V <sub>CC</sub> (device dependent)                   | 148   |

|   |      | 7.3.1 V <sub>CC</sub> monitor                                            | 149   |

|    |       | 7.3.2 Case temperature monitor                                                                   | 150 |

|----|-------|--------------------------------------------------------------------------------------------------|-----|

|    |       | 7.3.3 Example on evaluation of V <sub>CC</sub> , T <sub>CASE</sub> and diagnostic with SPC560Bxx | 151 |

|    |       |                                                                                                  | 131 |

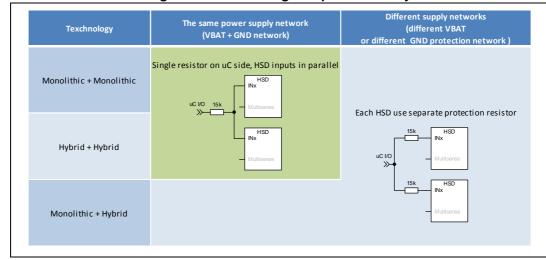

| 8  | Para  | lleling of devices                                                                               | 53  |

|    | 8.1   | Paralleling of logic input pins                                                                  | 153 |

|    |       | 8.1.1 Monolithic HSDs supplied from different supply lines                                       | 153 |

|    |       | 8.1.2 Hybrid HSDs supplied from different supply lines                                           | 155 |

|    |       | 8.1.3 Mix of monolithic and hybrid HSDs                                                          | 155 |

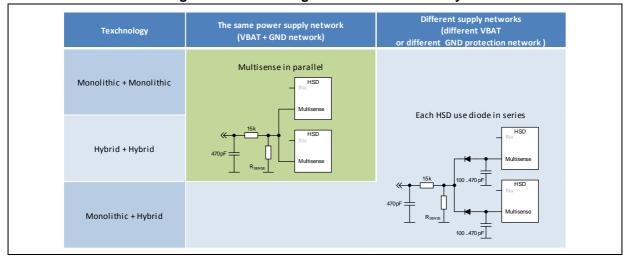

|    | 8.2   | Paralleling of MultiSense                                                                        | 158 |

|    |       | 8.2.1 Monolithic HSDs supplied from different supply lines                                       | 158 |

|    |       | 8.2.2 Hybrid HSDs supplied from different supply lines                                           | 159 |

|    |       | 8.2.3 Mix of monolithic and hybrid HSDs supplied from different supply lines                     |     |

|    |       |                                                                                                  | 160 |

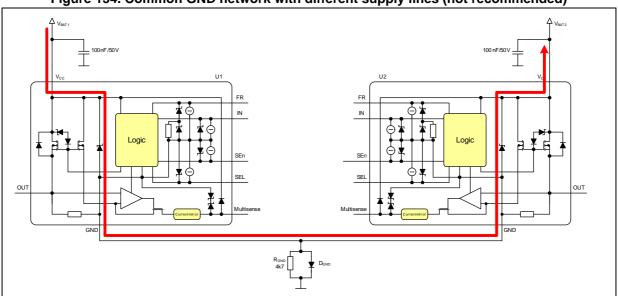

|    | 8.3   | Paralleling of GND protection network                                                            | 162 |

|    | 8.4   | Paralleling of outputs                                                                           | 163 |

|    |       | 8.4.1 Current balancing with resistive load                                                      | 163 |

|    |       | 8.4.2 Overload behavior with resistive loads                                                     | 165 |

|    |       | 8.4.3 Driving inductive loads                                                                    | 166 |

| 9  | Inver | se output current behavior1                                                                      | 72  |

|    | 9.1   | Introduction                                                                                     | 172 |

|    | 9.2   | Device capability versus inverse current                                                         | 173 |

|    |       | 9.2.1 Device in steady state                                                                     |     |

|    |       | 9.2.2 Device driven in PWM                                                                       | 178 |

|    | 9.3   | Conclusions                                                                                      | 179 |

| 10 | FSD   | protection                                                                                       | ເຂດ |

| 10 | 10.1  | EMC requirements for ESD at module level                                                         |     |

|    |       | ·                                                                                                |     |

|    | 10.2  | EMC Requirements for ESD at device level                                                         |     |

|    | 10.3  | Design and layout basic suggestions to increase ESD failure point level                          | 184 |

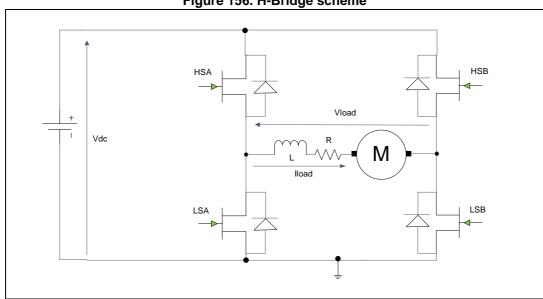

| 11 | Usag  | e in "H-Bridge" configurations                                                                   | 85  |

|    | 11.1  | Introduction                                                                                     | 185 |

|    | 11.2  | M0-7 high-side drivers in "H-Bridges": specific considerations                                   | 186 |

|    |       | 11.2.1 Short circuit event to ground and to battery                                              | 186 |

|    |       | 11.2.2 Cross current events                                                                      | 186 |

|    |       |                                                                                                  |     |

| UM1922       |           |                                         | Contents |

|--------------|-----------|-----------------------------------------|----------|

|              | 11.2.3    | Usage of MultiSense TCHIP in H-Bridges  | 191      |

|              | 11.2.4    | Freewheeling current of inductive loads | 191      |

| Appendix A   | Reference | es                                      | 194      |

| Revision his | tory      |                                         | 195      |

List of tables UM1922

# List of tables

| Table 1.  | Reverse battery protection concepts                                                                                             | . 16 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------|------|

| Table 2.  | Reverse battery-voltages on pins (VND7040AJ)                                                                                    | . 19 |

| Table 3.  | Static reverse battery - voltages on pins                                                                                       | . 26 |

| Table 4.  | Static reverse battery - voltages on pins                                                                                       | . 30 |

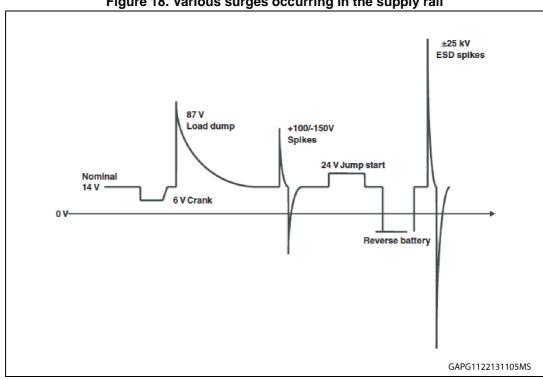

| Table 5.  | ISO 7637-2: 2004 (E)                                                                                                            | . 36 |

| Table 6.  | ISO 7637-2: 2011 (E)                                                                                                            |      |

| Table 7.  | ISO 7637-2 2004 and 2011 tests and results on monolithic HSDs                                                                   | . 41 |

| Table 8.  | GND network proposals for Hybrids HSDs                                                                                          | . 45 |

| Table 9.  | ISO 7637-2 levels and results for Hybrid HSDs                                                                                   | . 47 |

| Table 10. | M0-7 HSD devices not featuring latch-off functionality and FaultRST pin                                                         | . 48 |

| Table 11. | Truth table                                                                                                                     |      |

| Table 12. | MultiSense multiplexer addressing for a dual channel device                                                                     | . 49 |

| Table 13. | Classification of M0-7 HSDs                                                                                                     | . 57 |

| Table 14. | Full logic implementation                                                                                                       | . 58 |

| Table 15. | Reduced logic implementation (only current sense signal, no TCHIP, no VCC)                                                      | . 59 |

| Table 16. | Truth table for monolithic devices, separate MultiSense                                                                         | . 60 |

| Table 17. | Truth table for monolithic devices, common MultiSense                                                                           | . 61 |

| Table 18. | Truth table monolithic + hybrid, separate MultiSense                                                                            | . 63 |

| Table 19. | Truth table hybrid devices separate supply rails, common MultiSense                                                             | . 64 |

| Table 20. | Typical bulb loads for given M0-7 RON class                                                                                     | . 65 |

| Table 21. | VND7040AJ measurement of switching losses versus L in steady state                                                              | . 90 |

| Table 22. | VND7040AJ measurement of switching losses versus L in PWM mode (with external                                                   |      |

|           | freewheeling)                                                                                                                   | . 90 |

| Table 23. | Maximum capacitance on the HSD output (no power limitation triggered - T <sub>jstart</sub> ~ 25 °C)                             | 93   |

| Table 24. | Paralleling bulbs – overview on the example of VND7020AJ                                                                        | 130  |

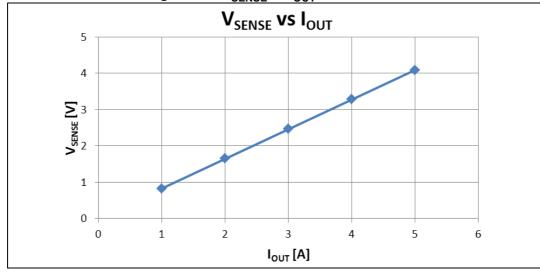

| Table 25. | V <sub>SENSE</sub> measurement                                                                                                  | 133  |

| Table 26. | MultiSense pin levels in off-state                                                                                              | 139  |

| Table 27. | Diagnostics - overview                                                                                                          | 140  |

| Table 28. | SPC560Bxx example signals mapping                                                                                               |      |

| Table 29. | Example of channels configuration on a dual channels HSD                                                                        | 174  |

| Table 30. | Inverse current threshold experimental values according to channels status (Ch0 is the                                          |      |

|           | channel under test, Ch0 = ON)                                                                                                   | 175  |

| Table 31. | Inverse current threshold experimental values according to channels status (Ch0 is the                                          |      |

|           | channel under test, Ch0 = OFF)                                                                                                  | 176  |

| Table 32. | M0-7 HSDs ESD results                                                                                                           |      |

| Table 33. | Maximum switching slopes which do not cause cross current due to MOSFETs capacitan (measurements on a sample on each component) |      |

| Table 34  | Document revision history                                                                                                       |      |

UM1922 List of figures

# List of figures

| Figure 1.  | Typical application schematics – monolithic devices                                                                                | . 12 |

|------------|------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.  | Typical application schematics – hybrid devices                                                                                    |      |

| Figure 3.  | Voltage levels during reverse battery (diode + resistor protection)                                                                | . 18 |

| Figure 4.  | Negative GND shift (TDEMAG > tD_STBY)                                                                                              | . 21 |

| Figure 5.  | GND resistor requirements (inductive load)—test setup                                                                              | . 22 |

| Figure 6.  | Measurement example (t <sub>DEMAG</sub> > t <sub>D_STBY</sub> ) without GND resistor                                               | . 22 |

| Figure 7.  | Measurement example (tDEMAG > tD_STBY) with 4.7 kΩ GND resistor                                                                    |      |

| Figure 8.  | Generic schematic and test setup with N-channel MOSFET in GND line                                                                 | . 26 |

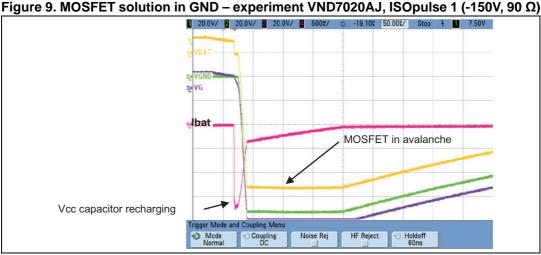

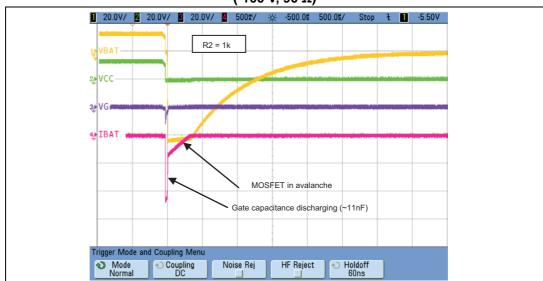

| Figure 9.  | MOSFET solution in GND – experiment VND7020AJ, ISOpulse 1 (-150V, 90 $\Omega$ )                                                    | . 27 |

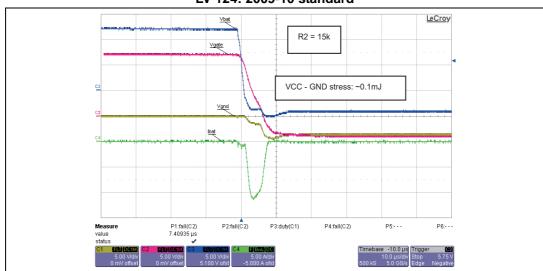

| Figure 10. | Reverse battery test VN7016AJ (13.5 V $\rightarrow$ -4 V, 82 m $\Omega$ , R2 = 15 k $\Omega$ ) as per LV 124:                      |      |

|            | 2009-10 standard                                                                                                                   |      |

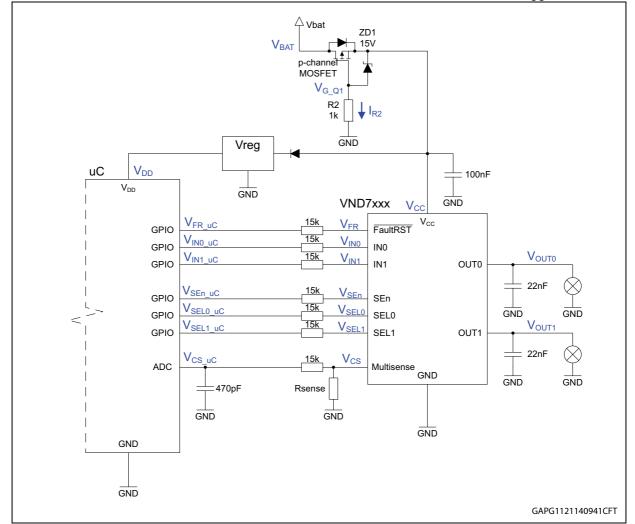

| Figure 11. | Generic schematic and test setup with P-channel MOSFET in V <sub>CC</sub> line                                                     | . 29 |

| Figure 12. | MOSFET solution in $V_{CC}$ – experiment VND7020AJ, ISOpulse 1 (-100 V, 90 $\Omega$ )                                              | . 30 |

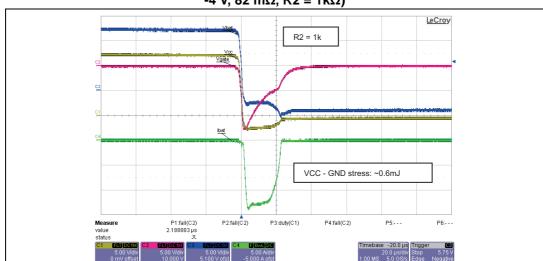

| Figure 13. | Reverse battery test according to LV 124:2009-10: VN7016AJ (13.5 V at -4 V, 82 mΩ,                                                 |      |

|            | $R2 = 1k\Omega) \dots \dots$ | . 31 |

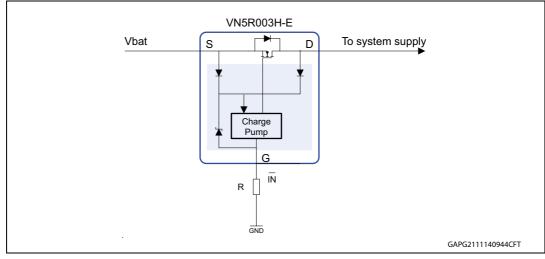

| Figure 14. | Reverse polarity protection – reverse FET protection                                                                               | . 32 |

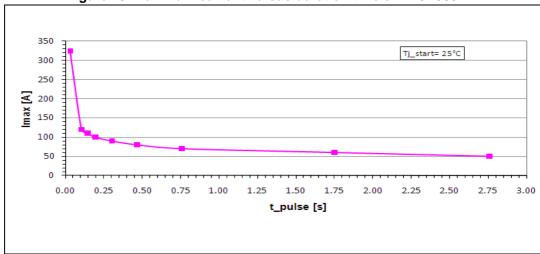

| Figure 15. | Maximum current versus duration time of VN5R003H-E                                                                                 | . 33 |

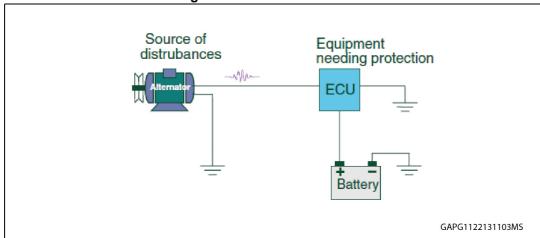

| Figure 16. | Conducted hazards                                                                                                                  | . 34 |

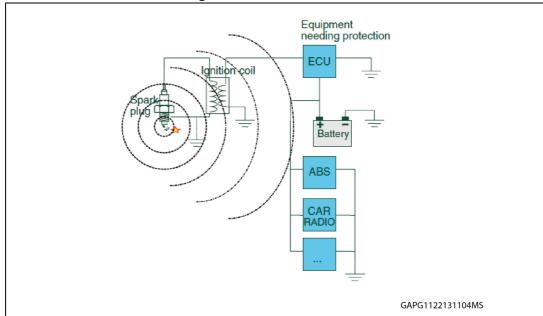

| Figure 17. | Radiated hazards                                                                                                                   |      |

| Figure 18. | Various surges occurring in the supply rail                                                                                        | . 36 |

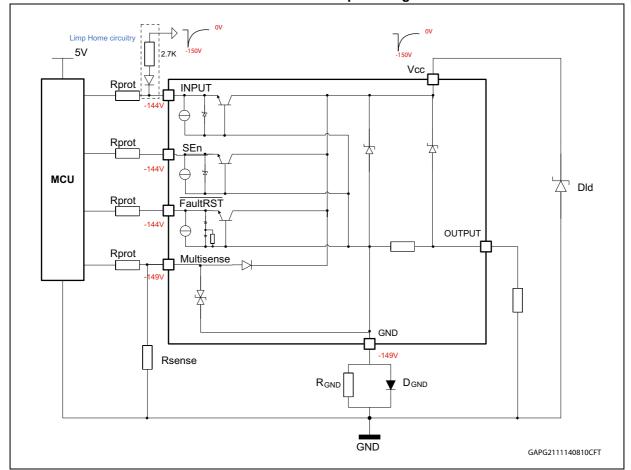

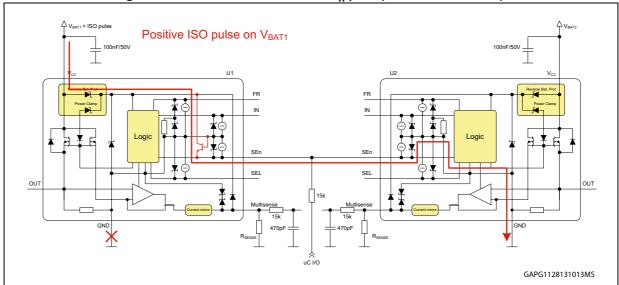

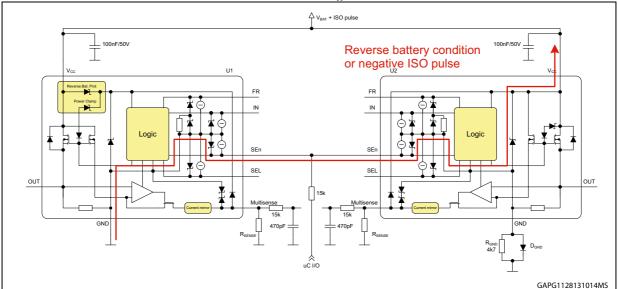

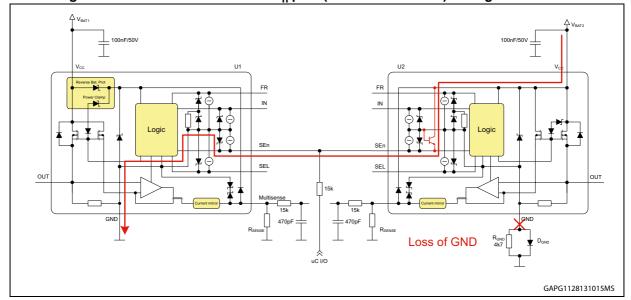

| Figure 19. | Internal structures involved during application of ISO 7637-2 pulse 1 in a monolithic HSI                                          | )    |

|            | and indication of pin voltages                                                                                                     | . 39 |

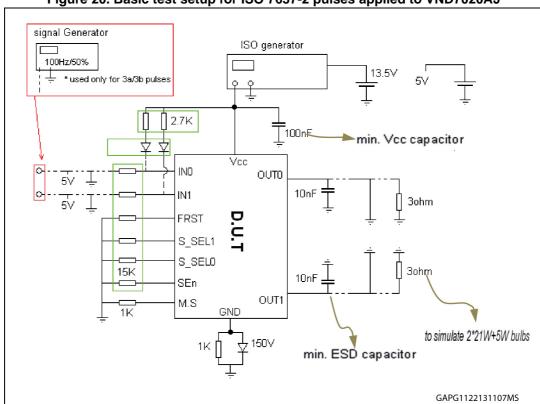

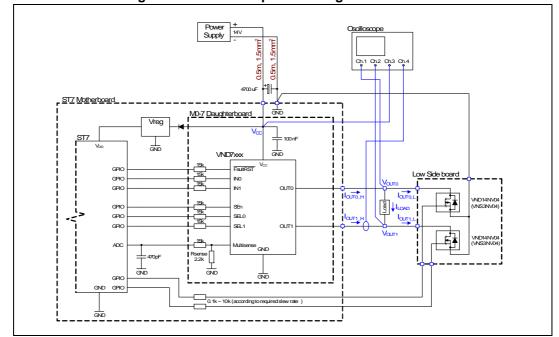

| Figure 20. | Basic test setup for ISO 7637-2 pulses applied to VND7020AJ                                                                        | . 40 |

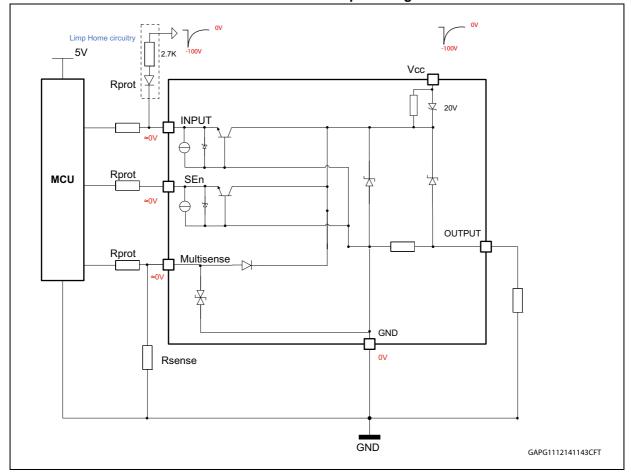

| Figure 21. | Internal structures involved during application of ISO 7637-2 (2004) pulse 1 in Hybrid HS                                          | SD   |

|            | and indication of pin voltages                                                                                                     |      |

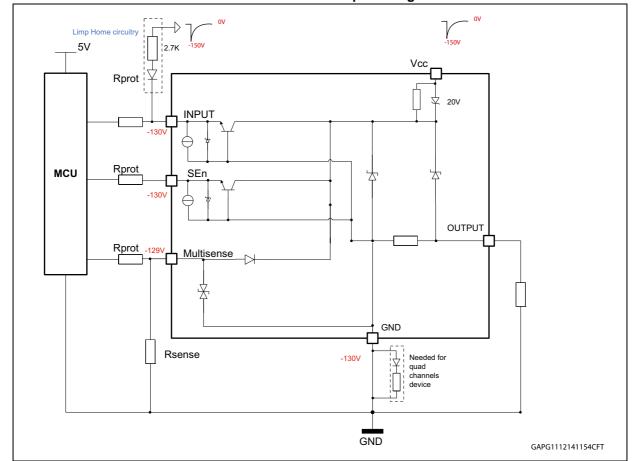

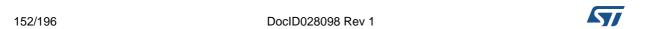

| Figure 22. | Internal structures involved during application of ISO 7637-2 (2011) pulse 1 in Hybrid HS                                          | SD   |

|            | and indication of pin voltages                                                                                                     | . 43 |

| Figure 23. | Basic test setup for ISO 7637-2 (2004) pulses applied to VN7004AH-E                                                                |      |

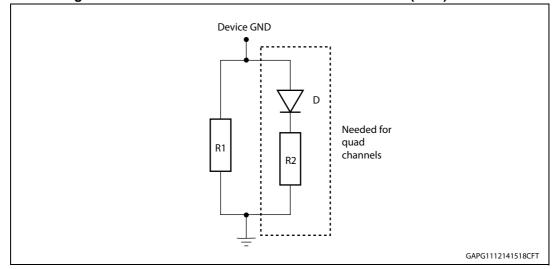

| Figure 24. | Recommended GND network for ISO 7637-2 (2011) level IV                                                                             |      |

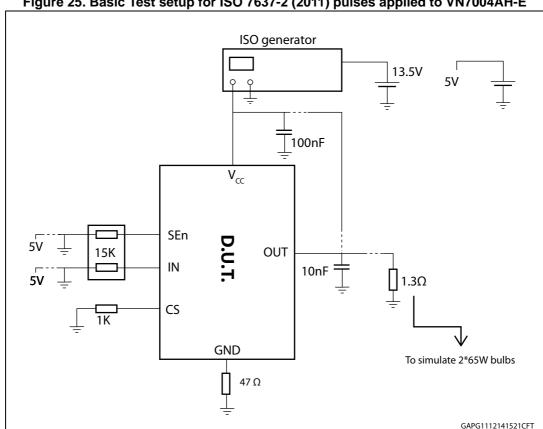

| Figure 25. | Basic Test setup for ISO 7637-2 (2011) pulses applied to VN7004AH-E                                                                |      |

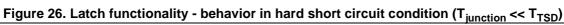

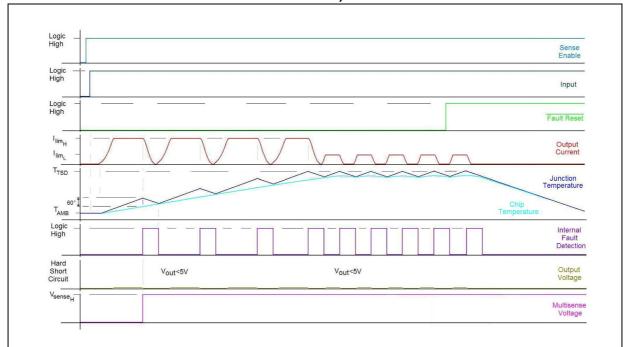

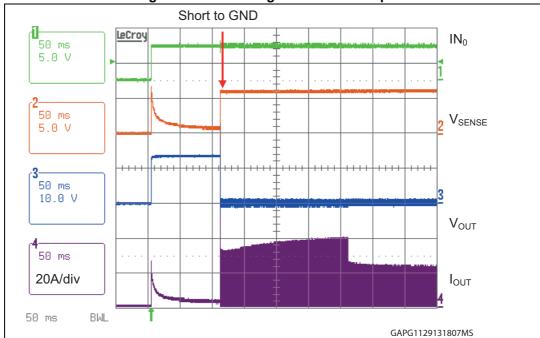

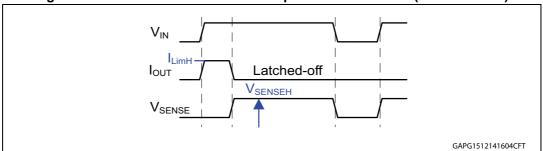

| Figure 26. | Latch functionality - behavior in hard short circuit condition (Tjunction << TTSD)                                                 |      |

| Figure 27. | Latch functionality - behavior in hard short circuit condition (TR < Tjunction < TTSD)                                             |      |

| Figure 28. | Latch functionality - behavior in hard short circuit condition (autorestart mode and latch-                                        | off) |

|            |                                                                                                                                    | _    |

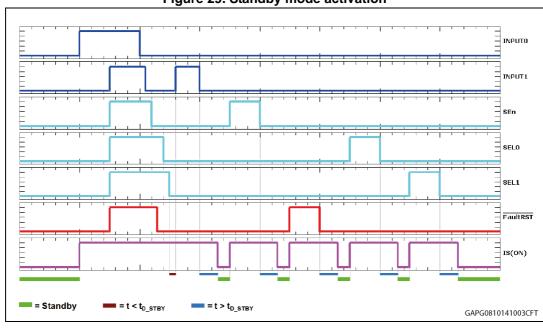

| Figure 29. | Standby mode activation                                                                                                            |      |

| Figure 30. | Standby state diagram                                                                                                              |      |

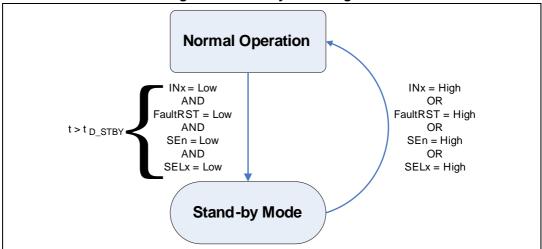

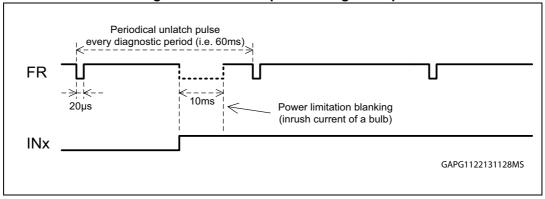

| Figure 31. | FR handling example - bulb inrush blanking (VNQ7140AJ)                                                                             | . 53 |

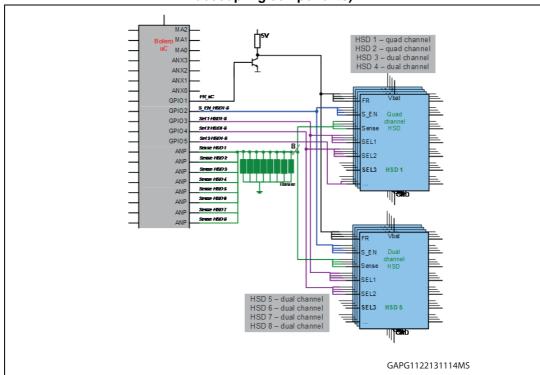

| Figure 32. | Common FaultRST pin handling example – basic schematic (without decoupling components)                                             | . 54 |

| Figure 33. | FaultRST pin handling concept                                                                                                      |      |

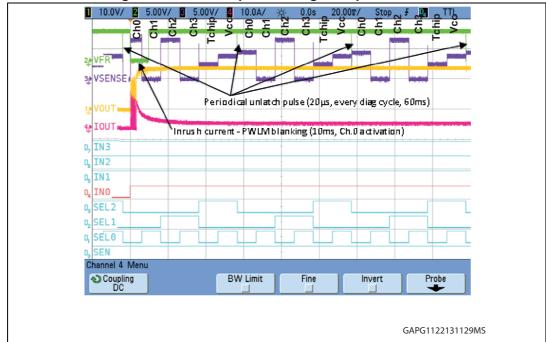

| Figure 34. | FaultRST pin handling example - overview                                                                                           |      |

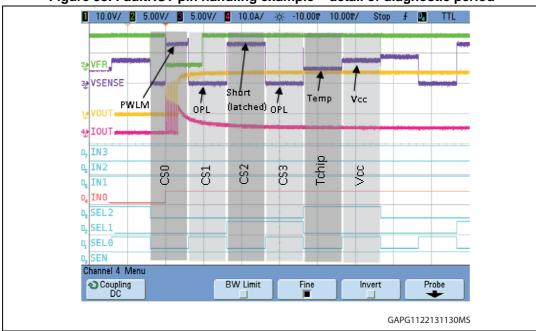

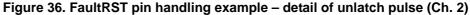

| Figure 35. | FaultRST pin handling example – detail of diagnostic period                                                                        |      |

| Figure 36. | FaultRST pin handling example – detail of unlatch pulse (Ch. 2)                                                                    |      |

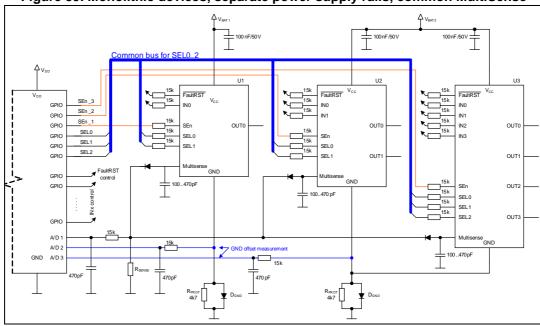

| Figure 37. | Monolithic devices, common power supply rails, separate MultiSense                                                                 |      |

| Figure 38. | Monolithic devices, common power supply rails, common MultiSense                                                                   |      |

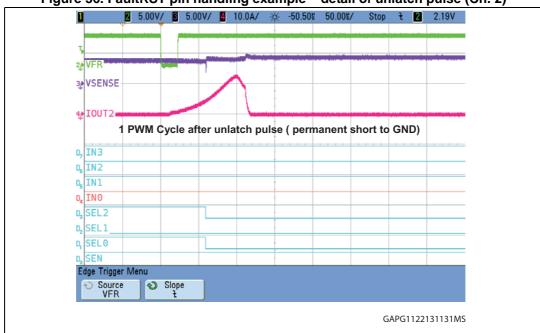

| Figure 39. | Monolithic devices, separate power supply rails, common MultiSense                                                                 |      |

| Figure 40. | Monolithic and hybrid device, separate power supply rails, separate MultiSense                                                     |      |

| Figure 41. | Hybrid devices, separate power supply rails, common MultiSense                                                                     |      |

| _          | · · · · · · · · · · · · · · · · · · ·                                                                                              |      |

List of figures UM1922

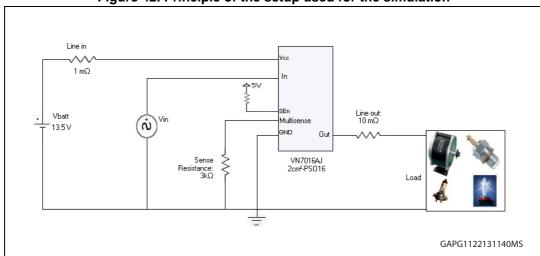

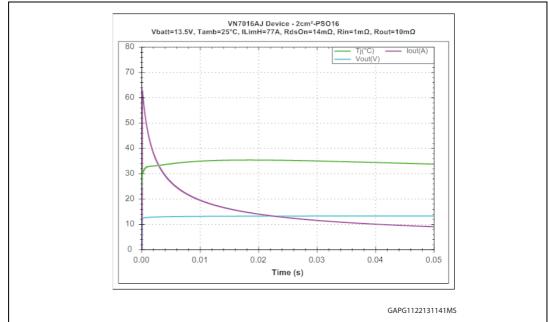

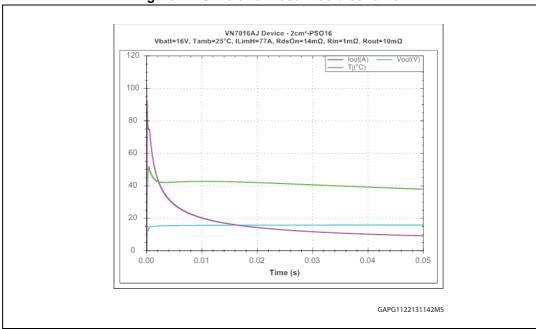

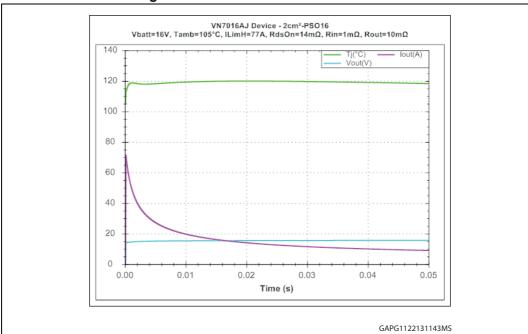

| Figure 42.<br>Figure 43. | Principle of the setup used for the simulation                                                 |       |

|--------------------------|------------------------------------------------------------------------------------------------|-------|

| •                        | Simulation result–cold condition                                                               |       |

| Figure 44.<br>Figure 45. | Simulation result–hot condition                                                                |       |

| •                        | Control stage current consumption in ON state, all channels on driving nominal load -          | 00    |

| Figure 46.               | · · · · · · · · · · · · · · · · · · ·                                                          | 60    |

| Figure 47.               | datasheet value)                                                                               |       |

| •                        |                                                                                                |       |

| Figure 48.               | RON dependency on temperature (measured on a VND7140AJ sample)                                 |       |

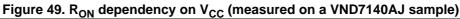

| Figure 49.               | RON dependency on VCC (measured on a VND7140A J sample)                                        |       |

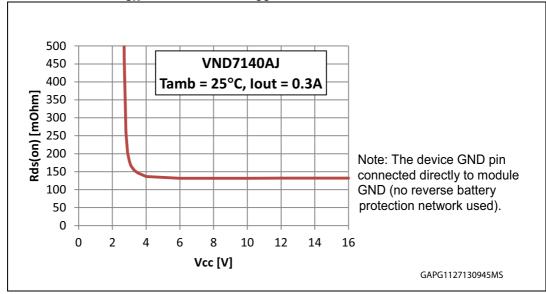

| Figure 50.               | RON dependency on IOUT (measured on a VND7140AJ sample)                                        |       |

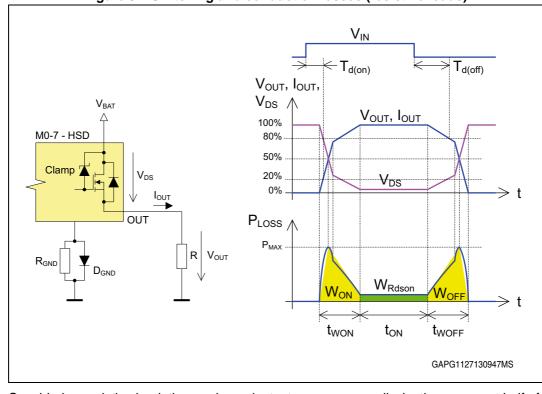

| Figure 51.               | Switching and conduction losses (resistive loads)                                              |       |

| Figure 52.               | ,                                                                                              |       |

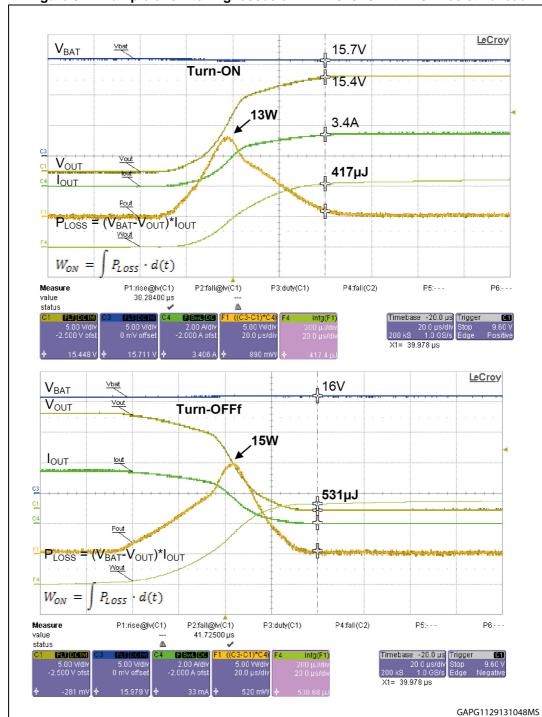

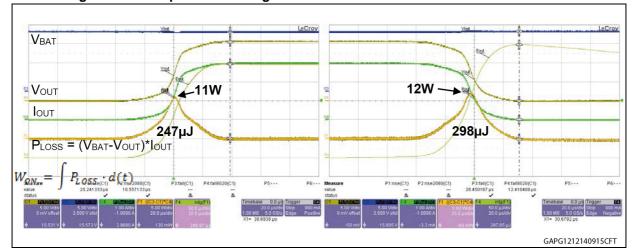

| Figure 53.               | Example of switching losses on VNQ7040AY with 5.2 Ω resistive load                             |       |

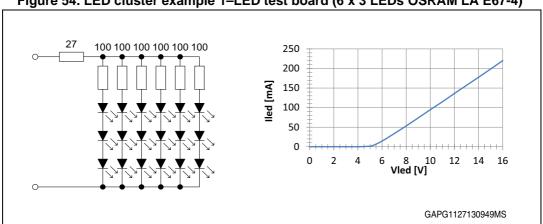

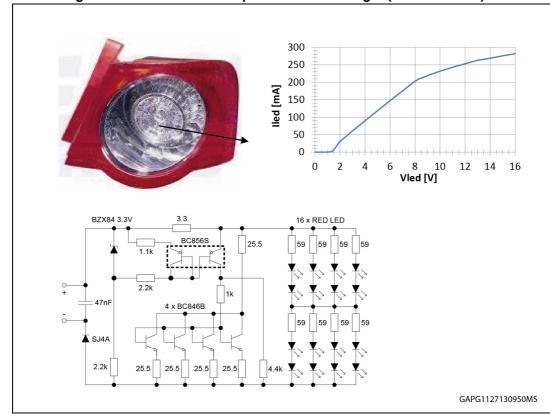

| Figure 54.               | LED cluster example 1–LED test board (6 x 3 LEDs OSRAM LA E67-4)                               |       |

| Figure 55.               | LED cluster example 2–tail & brake light (VW Passat B6)                                        |       |

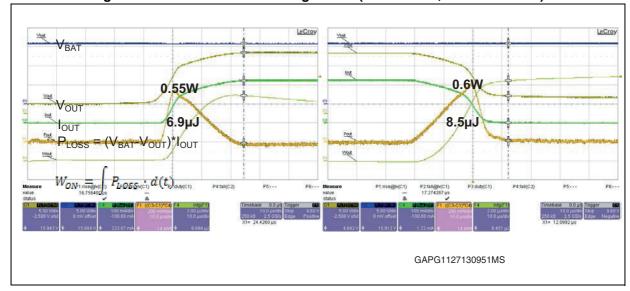

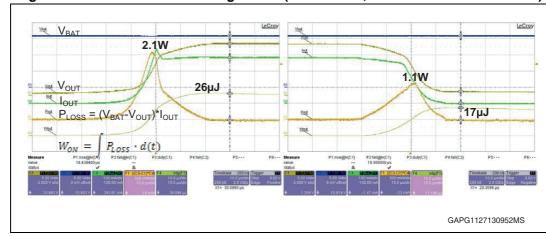

| Figure 56.               | Slew rate and switching losses (VND7140AJ, LED test board)                                     |       |

| Figure 57.               | Slew rate and switching losses (VND7140AJ, VW Passat B6–tail & brake)                          |       |

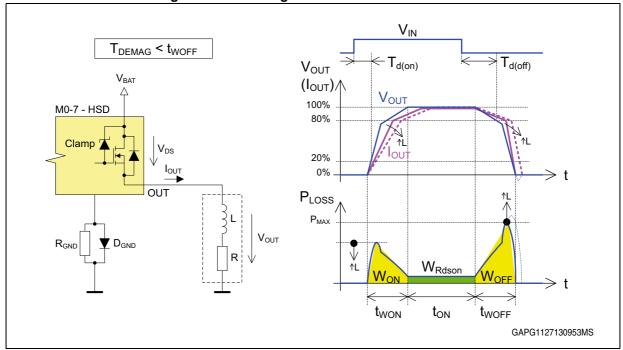

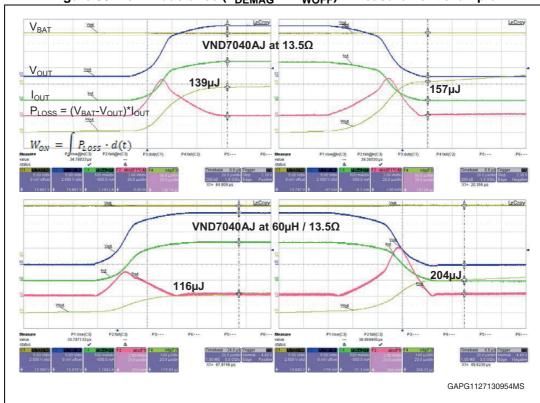

| Figure 58.               | Switching losses with low inductance                                                           |       |

| Figure 59.               | Low inductance (TDEMAG << t <sub>WOFF</sub> ) – measurement example                            |       |

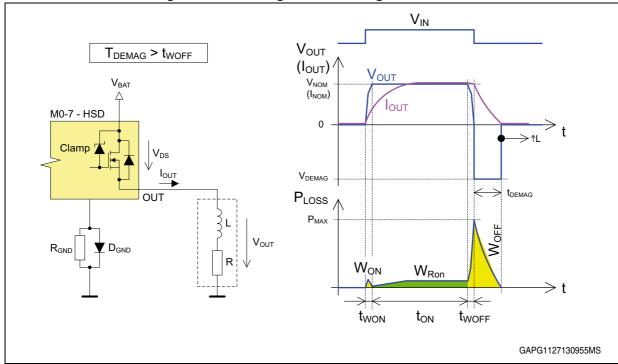

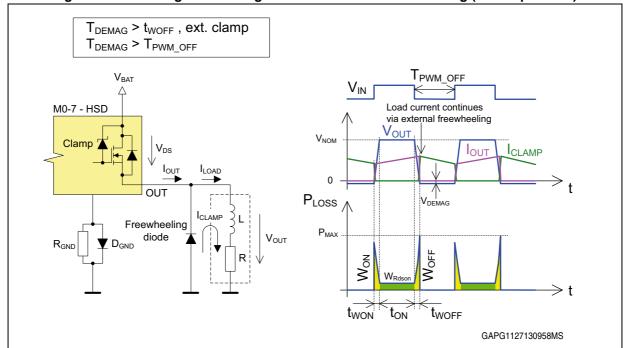

| Figure 60.               | Switching losses with high inductance                                                          |       |

| Figure 61.               | High inductance (TDEMAG >> t <sub>WOFF</sub> ) – measurement example                           |       |

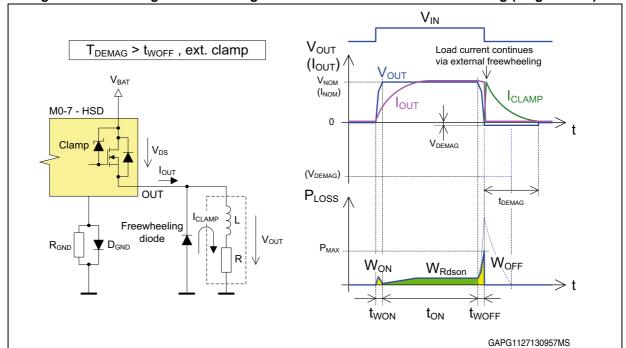

| Figure 62.               | Switching losses with high inductance and external freewheeling (single event)                 |       |

| Figure 63.               | Switching losses – high inductance + ext. freewheeling (PWM operation)                         |       |

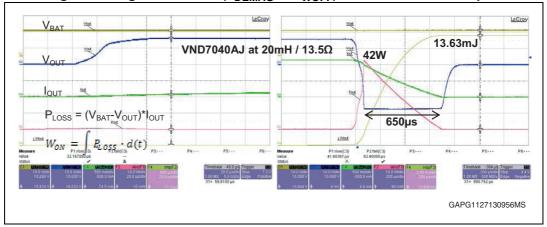

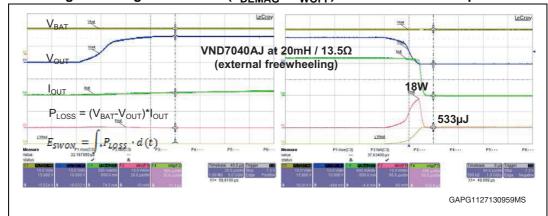

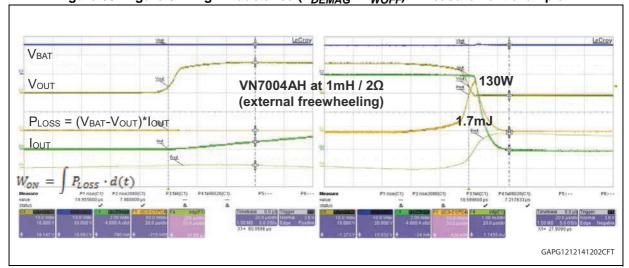

| Figure 64.               | High inductance (TDEMAG > t <sub>WOFF</sub> ): measurement example 1                           |       |

| Figure 65.               | Figure 62: High inductance (T <sub>DEMAG</sub> > t <sub>WOFF</sub> ) – measurement example 2   |       |

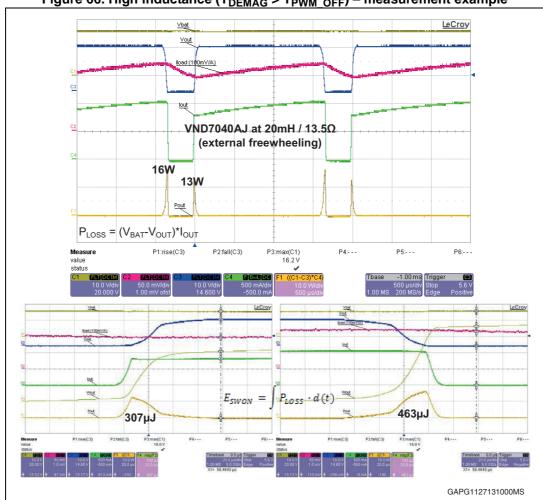

| Figure 66.               | High inductance (T <sub>DEMAG</sub> > T <sub>PWM_OFF</sub> ) – measurement example             |       |

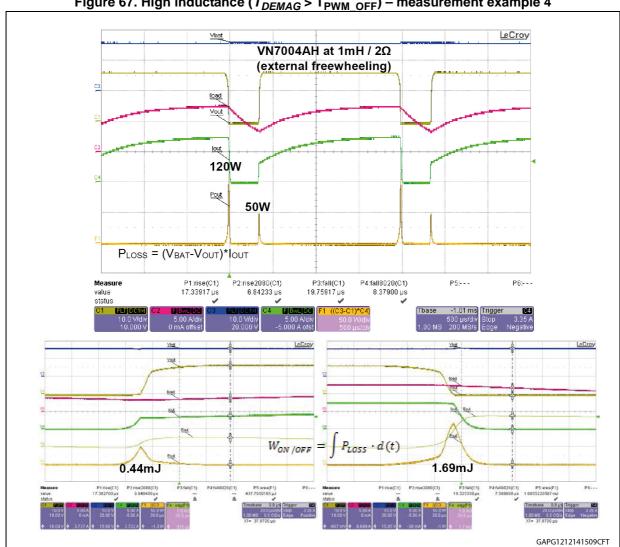

| Figure 67.               | High inductance (T <sub>DEMAG</sub> > T <sub>PWM_OFF</sub> ) – measurement example 4           |       |

| Figure 68.               | A typical example of HSD combined with capacitive load                                         |       |

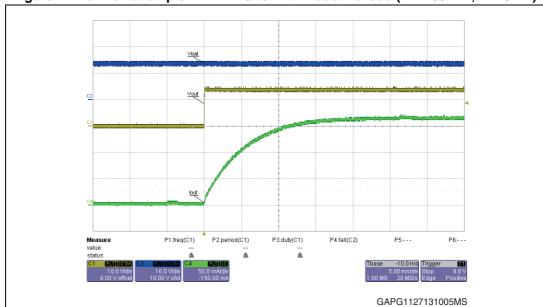

| Figure 69.               | Measurement example - VND7040AJ on 320µF                                                       |       |

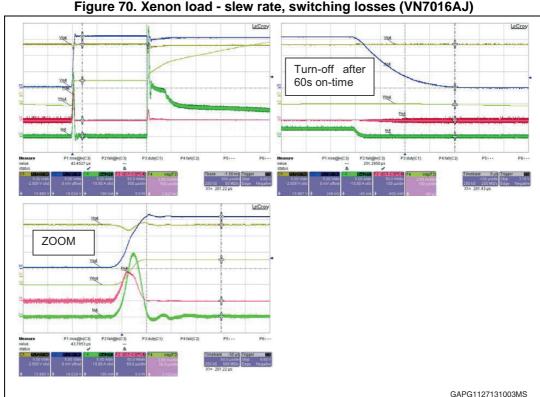

| Figure 70.               | Xenon load - slew rate, switching losses (VN7016AJ)                                            |       |

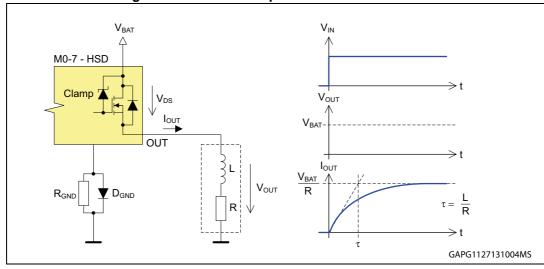

| Figure 71. Figure 72.    | HSD turn-on phase with inductive load                                                          |       |

|                          | Inductive load—HSD turn-off phase                                                              |       |

| Figure 73.               | Inductive load: turn-off example: VND7040AJ, L = 260 mH, R = 81 $\Omega$                       |       |

| Figure 74.               | Maximum turn-off current versus inductance – VND7020AJ datasheet                               |       |

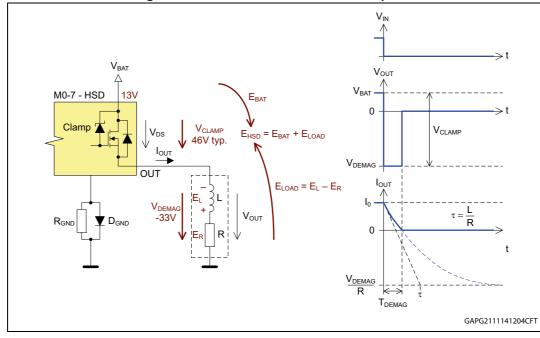

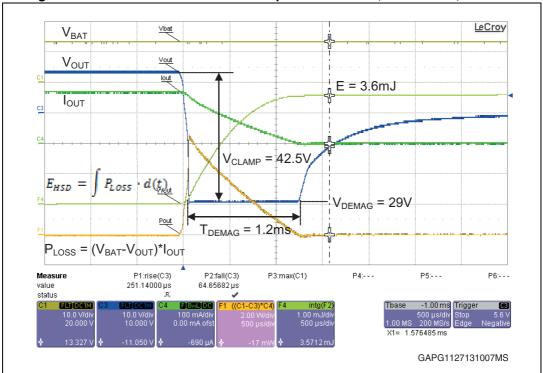

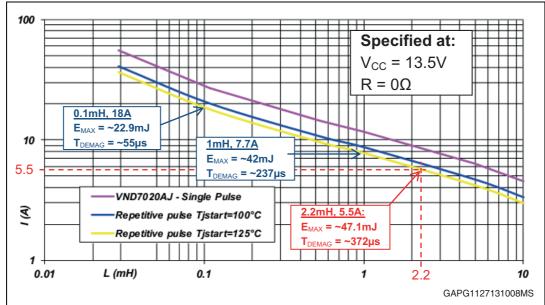

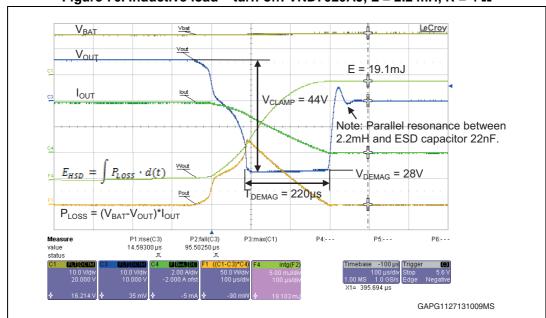

| Figure 75.<br>Figure 76. | Inductive load – turn-off: VND7020AJ, L = 2.2 mH, R = 4 $\Omega$                               |       |

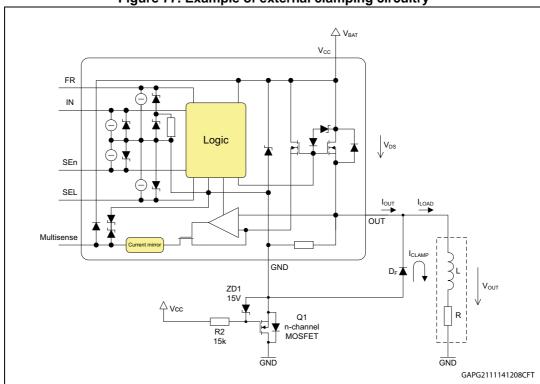

| Figure 75.               | Example of external clamping circuitry                                                         |       |

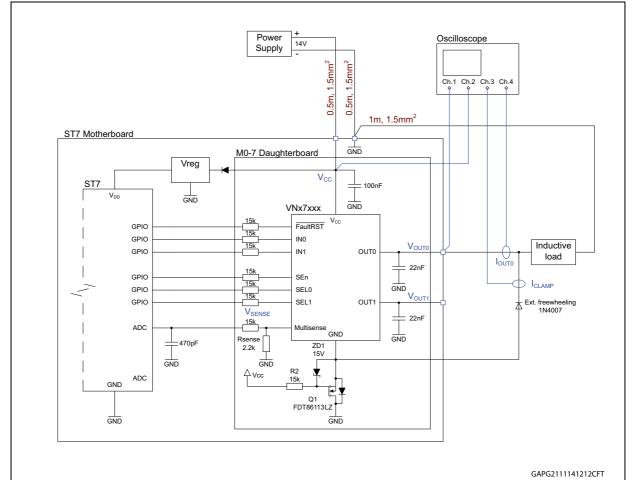

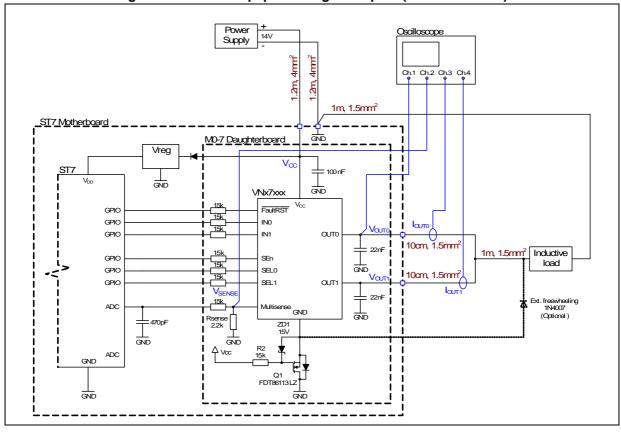

| -                        | Test setup-verification of new external clamp proposal                                         |       |

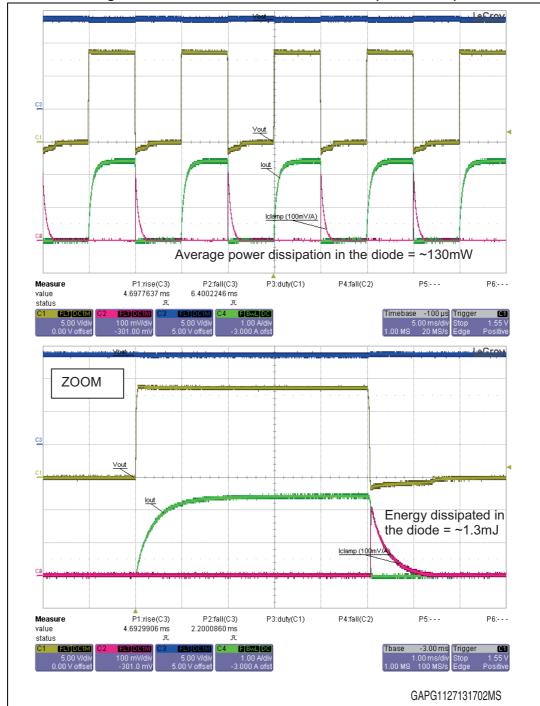

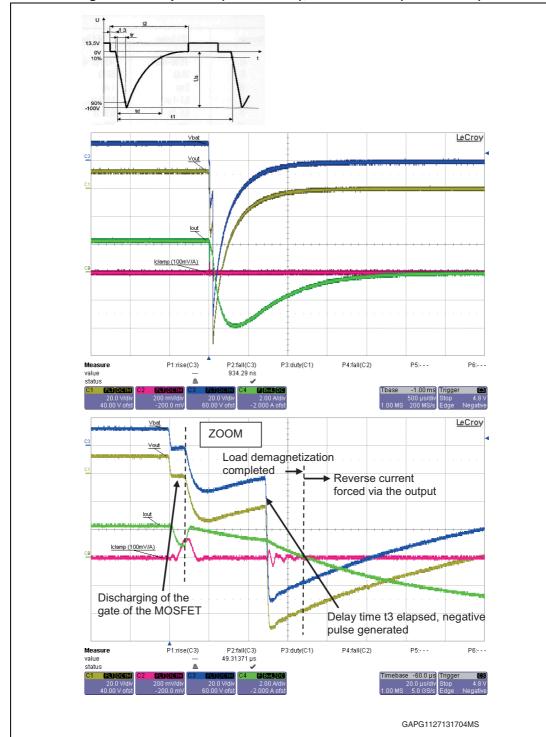

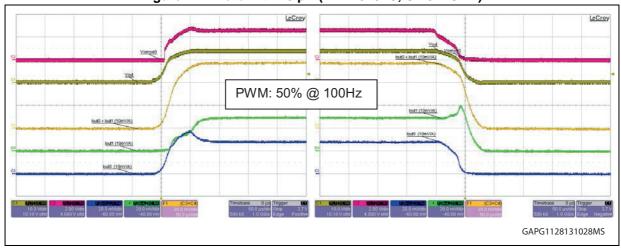

| Figure 78. Figure 79.    | PWM 50% at 100 Hz, 2 mH / 5.5 $\Omega$ (VND7040AJ)                                             |       |

| Figure 79.               | ,                                                                                              |       |

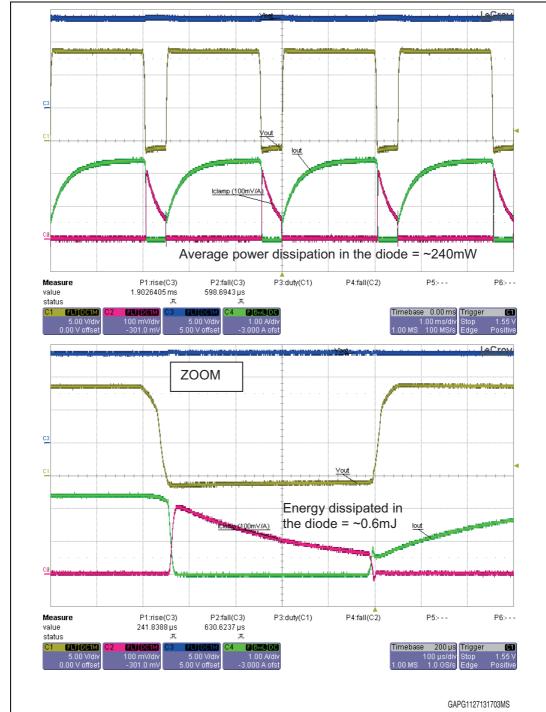

| Figure 81.               | PWM 80 % at 400 Hz, 2 mH / 5.5 Ω (VND7040AJ)                                                   |       |

| •                        |                                                                                                |       |

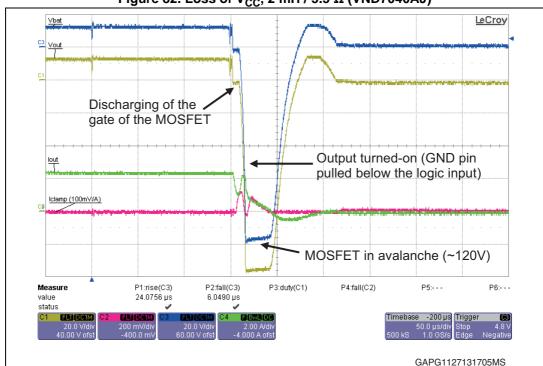

| Figure 82.<br>Figure 83. | Loss of $V_{CC}$ , 2 mH / 5.5 $\Omega$ (VND7040AJ)                                             |       |

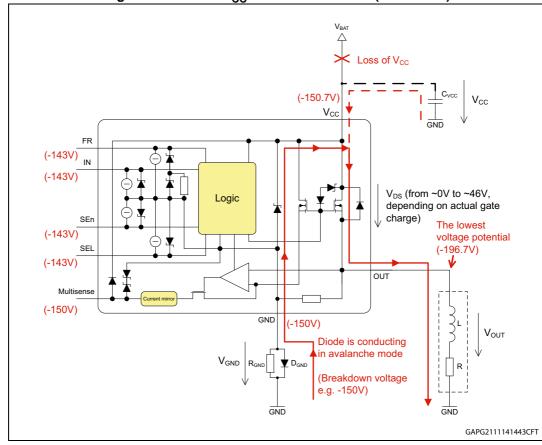

| •                        | Loss of V <sub>CC</sub> with inductive load (monolithic)                                       |       |

| Figure 84.               | Test setup – loss of V <sub>CC</sub> (monolithic)                                              |       |

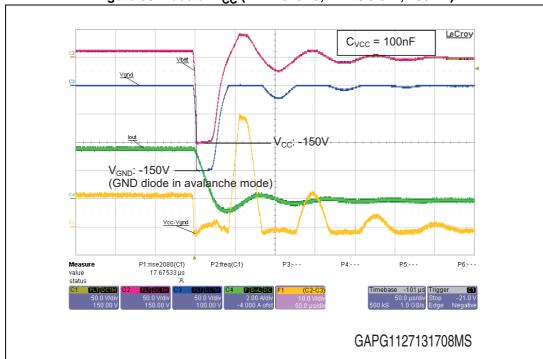

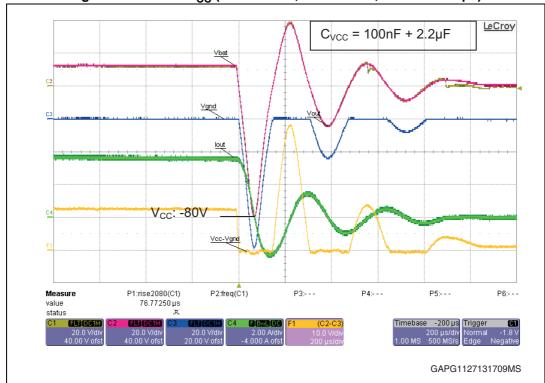

| Figure 85.               | Loss of $V_{CC}$ (VND7020AJ, 1 mH/ 3.5 $\Omega$ , 100 nF)                                      |       |

| Figure 86.               |                                                                                                |       |

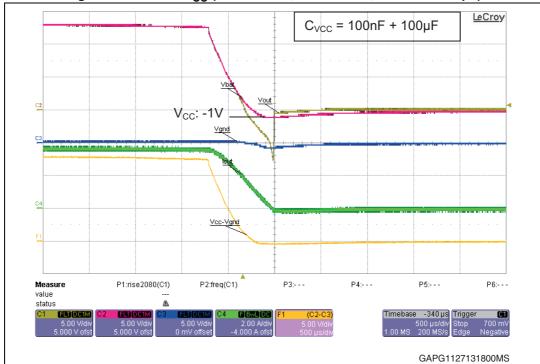

| Figure 87.               | Loss of $V_{CC}$ (VND7020AJ, 1 mH/ 3.5 $\Omega$ , 100 nF + 100 $\mu$ F)                        |       |

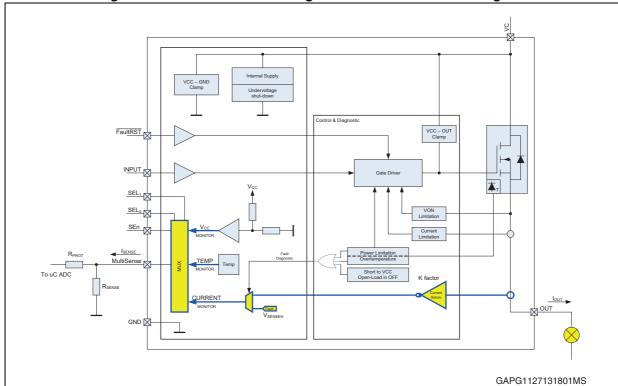

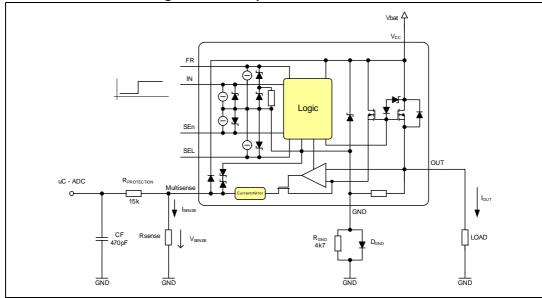

| Figure 88.               | M0-7 driver with analogue current sense – block diagram                                        |       |

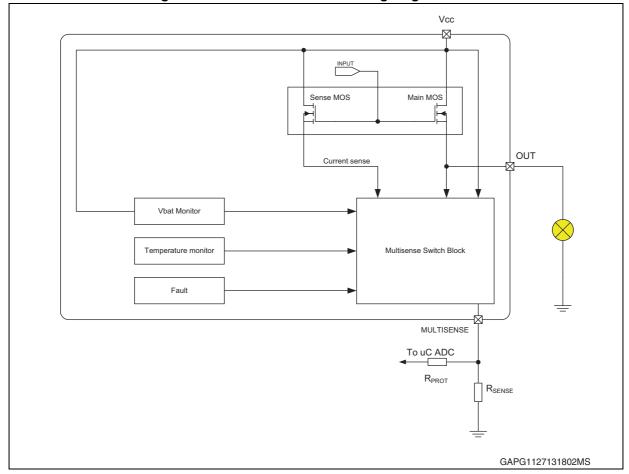

| Figure 89.<br>Figure 90. | Structure of MultiSense signal generation                                                      |       |

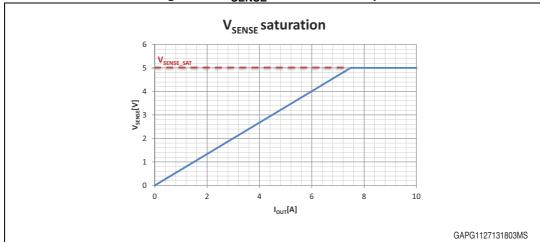

| Figure 90.               | $V_{SENSE}$ saturation example                                                                 | . 120 |

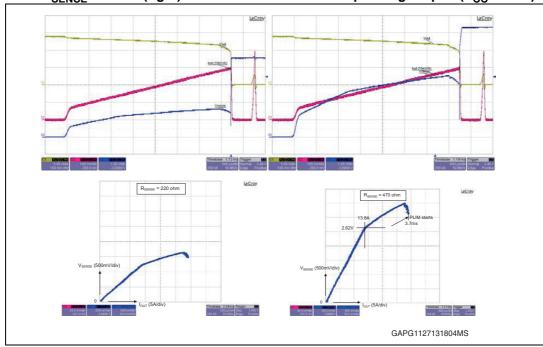

| i iguie a i.             | RSENSE = 470 $\Omega$ (right) for VND7040AJ and corresponding XY plot (V <sub>CC</sub> = 14 V) | 121   |

UM1922 List of figures

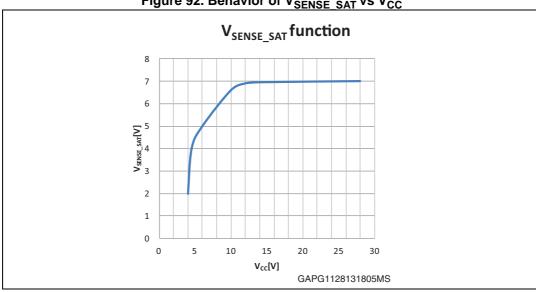

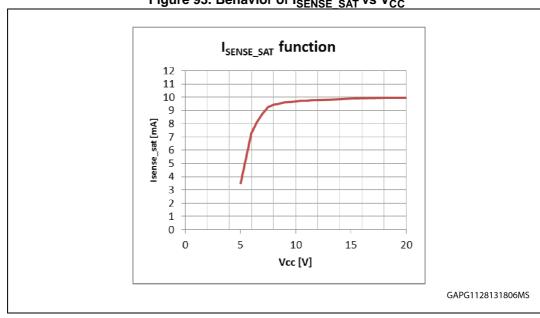

| Figure<br>Figure |      | Behavior of VSENSE_SAT vs $V_{CC}$                                                                  | 122 |

|------------------|------|-----------------------------------------------------------------------------------------------------|-----|

| Figure           |      | Failure flag indication-example 4                                                                   | 123 |

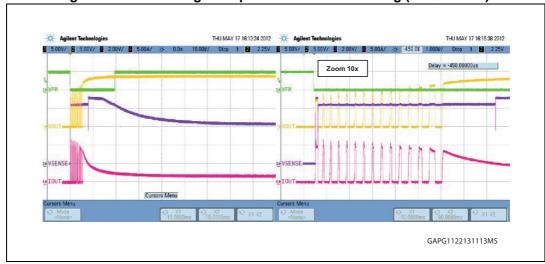

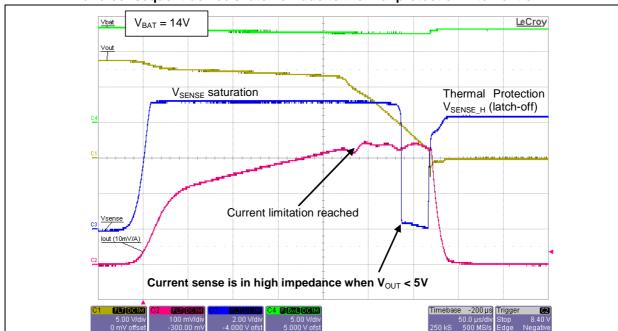

| Figure           | 95.  | MultiSense operation of VND7040AJ in current monitoring with increasing overload and                | 404 |

| F:               | 00   | consequent device's latch off due to thermal protection intervention                                |     |

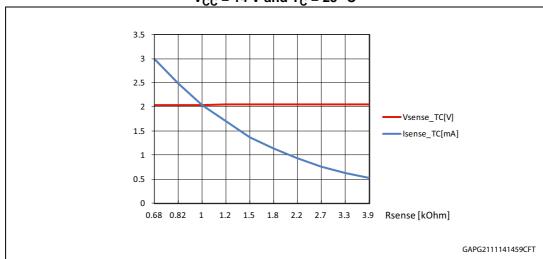

| Figure           | 96.  | MultiSense in TCHIP mode behavior versus RSENSE for VND7140AJ at $V_{CC}$ = 14 V and $TC$ = 25 °C   |     |

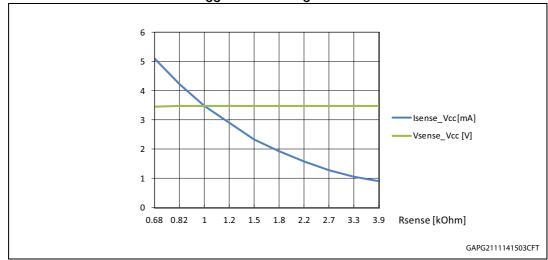

| Figure           | 97   | MultiSense in $V_{CC}$ mode behavior versus RSENSE for VND7140AJ at $V_{CC}$ = 14 V and             | 120 |

| i iguic          | 57.  | TC = 25 °C                                                                                          | 126 |

| Figure           | 98.  | Bulb / LED diagnostic example                                                                       |     |

| Figure           |      | Minimum ON time for correct V <sub>SENSE</sub> sampling                                             |     |

| _                |      | Switched current sense resistor—example                                                             |     |

|                  |      | Example of single point calibration at low current for VND7020AJ                                    |     |

| -                |      | V <sub>SENSE</sub> vs IOUT measurement                                                              |     |

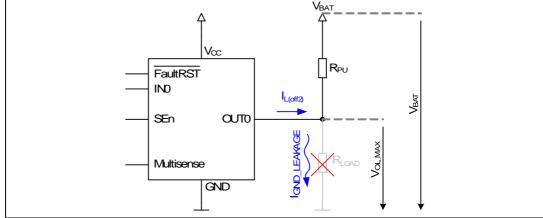

| Figure           | 103. | R <sub>PU</sub> calculation with no load connected                                                  | 136 |

| Figure           | 104. | R <sub>PU</sub> calculation with load connected                                                     | 137 |

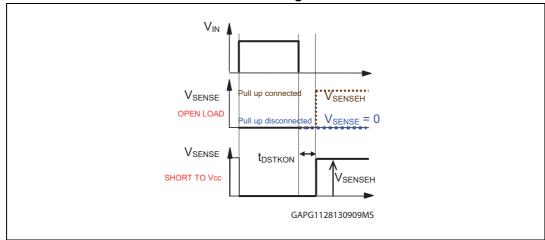

|                  |      | Analogue HSD – open load detection in off-state                                                     |     |

| Figure           | 106. | Open load / short to $V_{CC}$ detection in OFF state - delay after IN is set from low to high . 1   | 138 |

| Figure           | 107. | Open load/short to $V_{CC}$ detection in OFF state - delay after $SE_n$ is set from low to high . 1 | 139 |

|                  |      | Open-load without pull-up timings                                                                   |     |

| -                |      | Open-load with pull-up timings                                                                      |     |

|                  |      | Short circuit to V <sub>BATT</sub> timings                                                          |     |

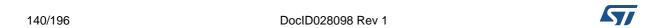

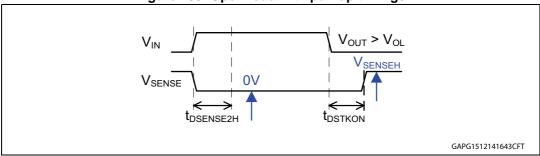

| -                |      | Power limitation or overtemperature waveforms (in autorestart mode)                                 |     |

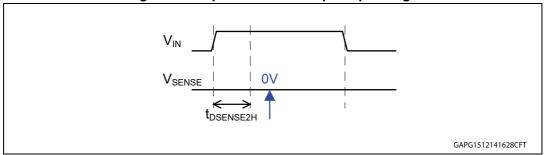

|                  |      | Power limitation or overtemperature waveforms (in lacth mode)                                       |     |

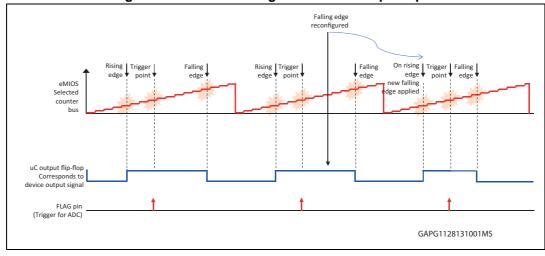

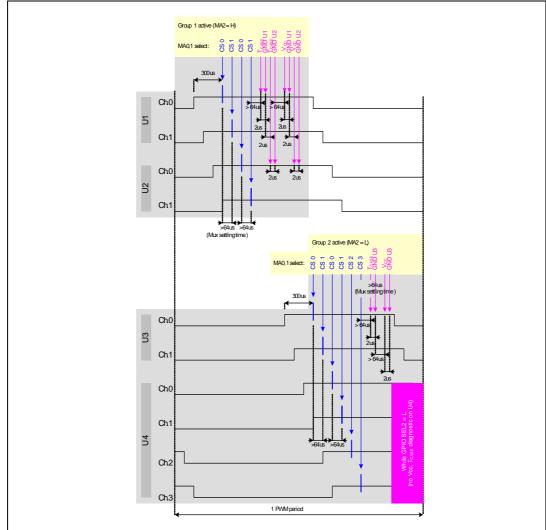

|                  |      | eMIOS PWM generation mode principle                                                                 |     |

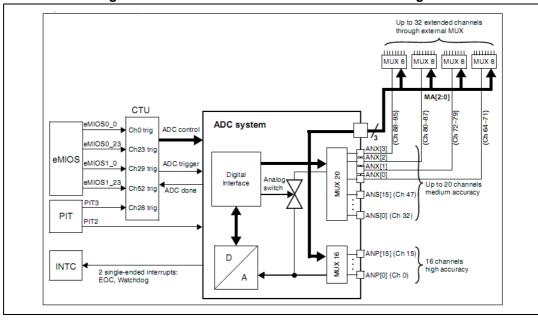

|                  |      | SPC extended ADC channels block diagram                                                             |     |

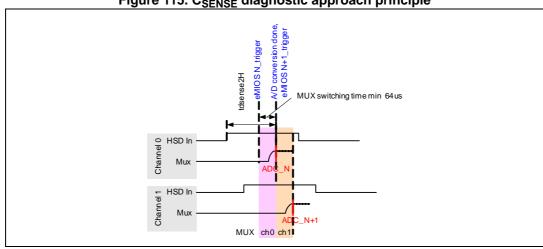

|                  |      | C <sub>SENSE</sub> diagnostic approach principle                                                    |     |

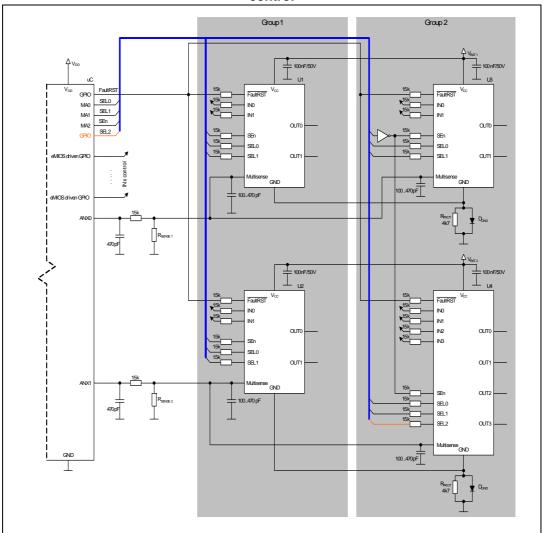

|                  |      | Example of connection of multiple HSDs to SPC using external ADC MUX control                        |     |

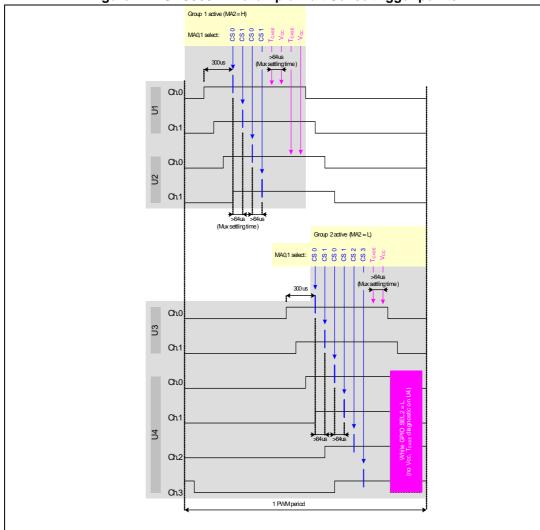

|                  |      | SPC560Bxx example MultiSense trigger points                                                         |     |

| _                |      | Low pass filter connection                                                                          |     |

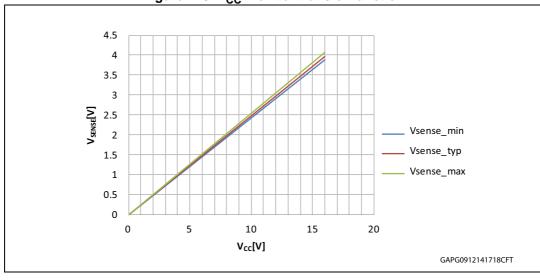

|                  |      | V <sub>CC</sub> monitor transfer function                                                           |     |

|                  |      | Example MultiSense reading on multiple HSDs with GND shift compensation                             |     |

|                  |      | GND shift measurement position example                                                              |     |

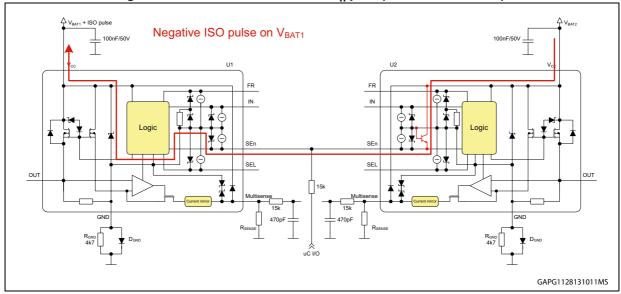

|                  |      | Direct connection of SE <sub>n</sub> pins (not recommended)                                         |     |

|                  |      | Proper connection of SE <sub>n</sub> pins                                                           |     |

|                  |      | Direct connection of SE <sub>n</sub> pins (not recommended)                                         |     |

| -                |      | Direct connection of SE <sub>n</sub> pins (not recommended)                                         |     |

|                  |      | Direct connection of SE <sub>n</sub> pins (not recommended) during loss of GND                      |     |

| Figure           | 128. | Paralleling of inputs summary                                                                       | 157 |

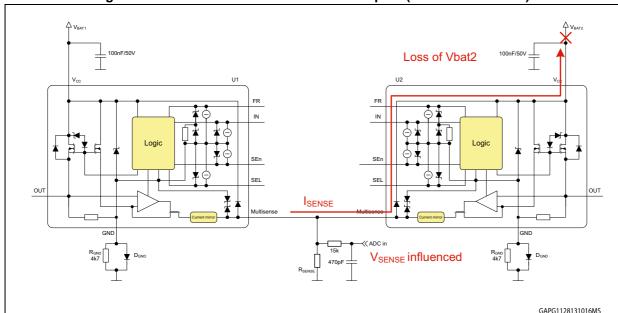

| Figure           | 129. | Direct connection of MultiSense pins (not recommended)                                              | 158 |

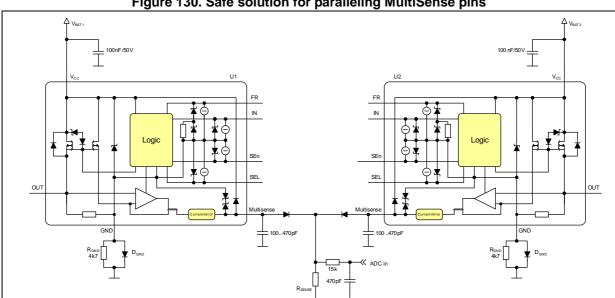

| Figure           | 130. | Safe solution for paralleling MultiSense pins                                                       | 159 |

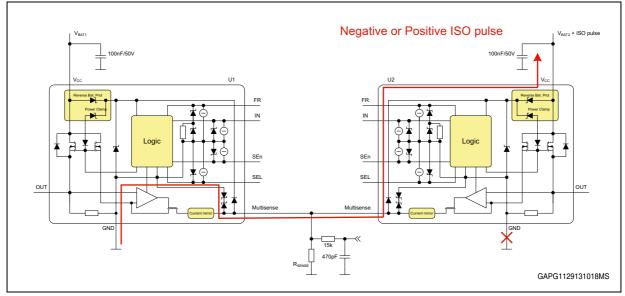

| Figure           | 131. | Direct connection of MultiSense pins (not recommended)                                              | 160 |

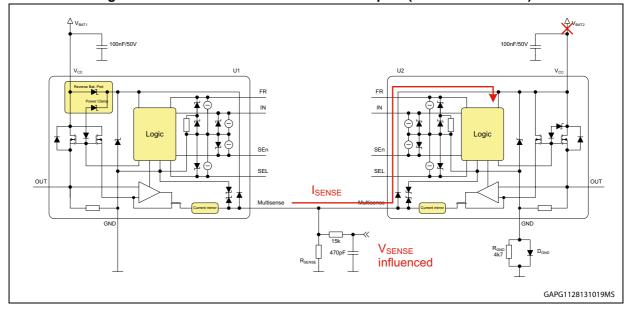

|                  |      | Direct connection of MultiSense pins (not recommended)                                              |     |

|                  |      | Paralleling of MultiSense summary                                                                   |     |

| Figure           | 134. | Common GND network with different supply lines (not recommended)                                    | 162 |

|                  |      | Test setup – paralleling of outputs (load current sharing)                                          |     |

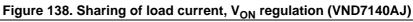

|                  |      | Sharing of load current, V <sub>ON</sub> regulation (VND7020AJ)                                     |     |

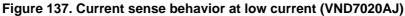

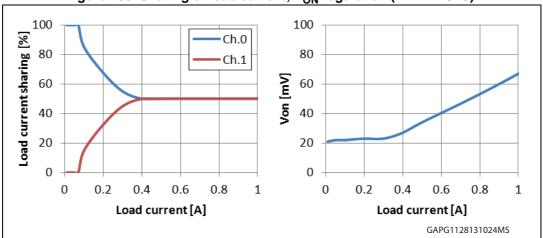

|                  |      | Current sense behavior at low current (VND7020AJ)                                                   |     |

|                  |      | Sharing of load current, V <sub>ON</sub> regulation (VND7140AJ)                                     |     |

|                  |      | Current sense behavior at low current (VND7140AJ)                                                   |     |

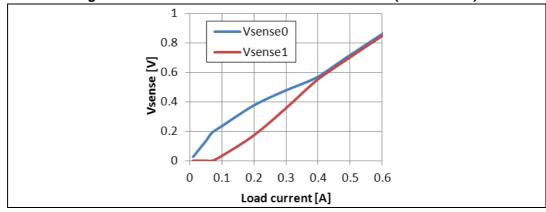

| Figure           | 140. | Behavior during overload condition (VND7040AJ, Ch.0 + Ch.1)                                         | 166 |

List of figures UM1922

|             | Test setup–paralleling of outputs (inductive loads)                                        |     |

|-------------|--------------------------------------------------------------------------------------------|-----|

| Figure 142. | Bulb with 10 μH (VND7040AJ, Ch.0 + Ch.1)                                                   | 167 |

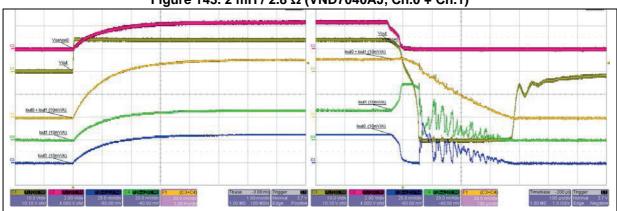

| Figure 143. | 2 mH / 2.8 $\Omega$ (VND7040AJ, Ch.0 + Ch.1)                                               | 168 |

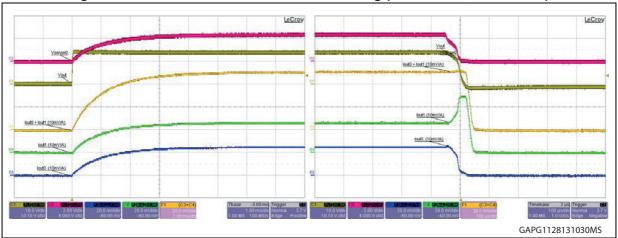

| Figure 144. | $2mH/2.8\Omega$ with external freewheeling (VND7040AJ, Ch.0 + Ch.1)                        | 168 |

| Figure 145. | Test setup – inductive short circuit test with paralleled outputs                          | 169 |

| Figure 146. | Inductive short – 5 $\mu$ H/50 m $\Omega$ (VND7020AJ, Ch0 and Ch1 in parallel, Latch mode) | 170 |

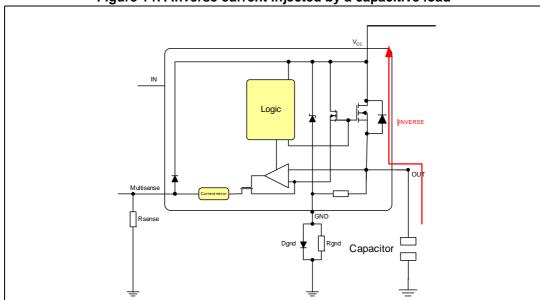

| Figure 147. | Inverse current injected by a capacitive load                                              | 172 |

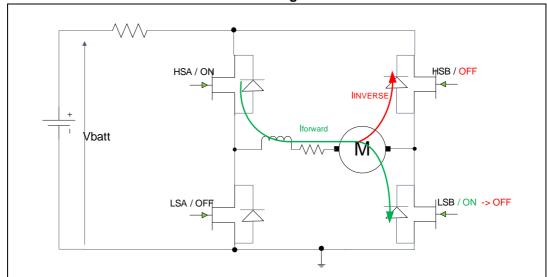

| Figure 148. | Inverse Current injected by an inductive load in the high-side driver of an H-Bridge       | 173 |

| Figure 149. | Inverse current Injected by a short circuit to battery                                     | 173 |

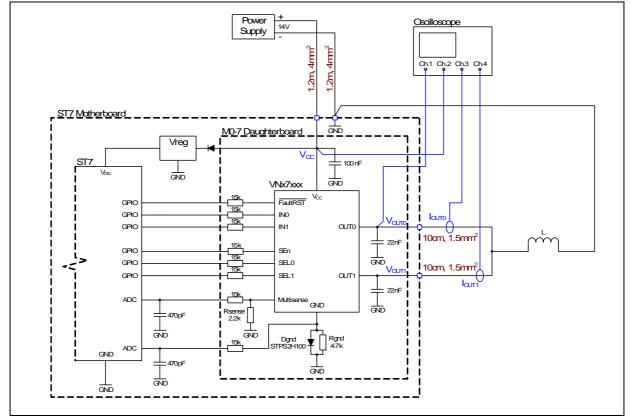

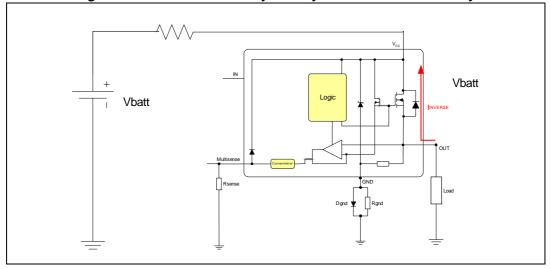

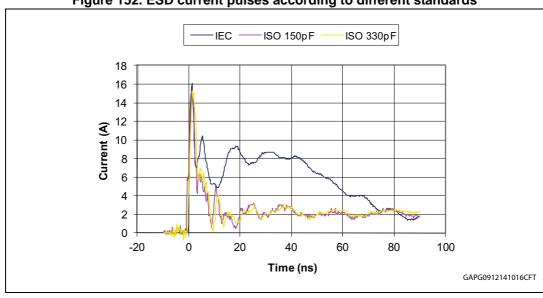

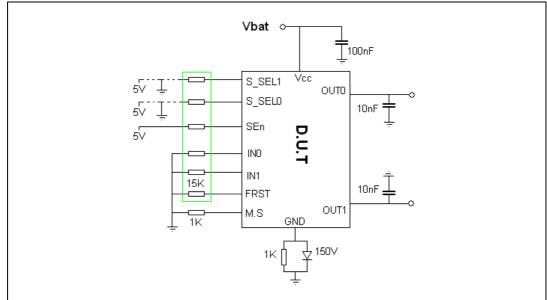

| Figure 150. | Current Injection test set-up and concerning a double channel HSD                          | 177 |

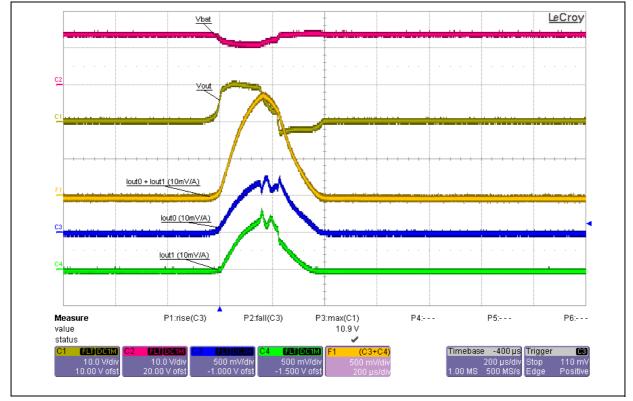

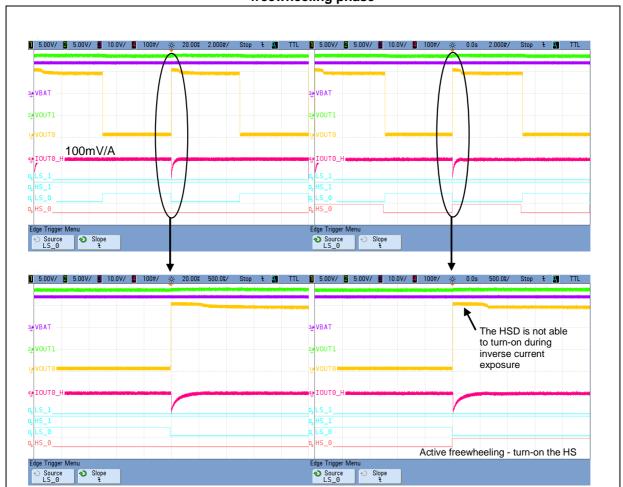

| Figure 151. | Waveforms related to the inverse injection on a channel driven in PMW                      | 178 |

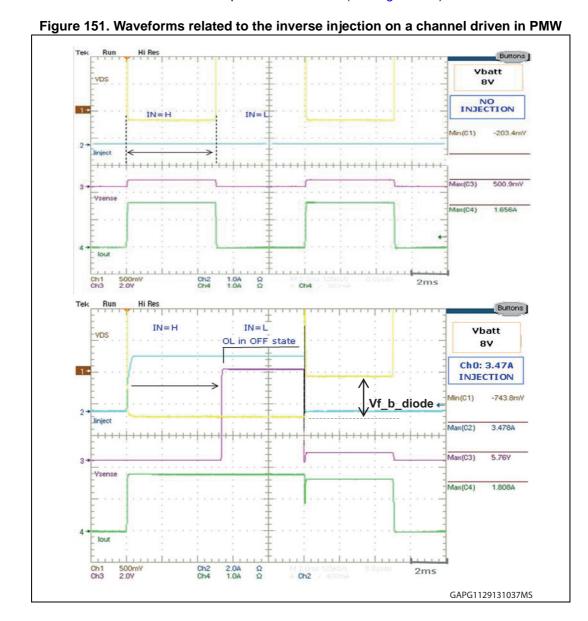

| Figure 152. | ESD current pulses according to different standards                                        | 180 |

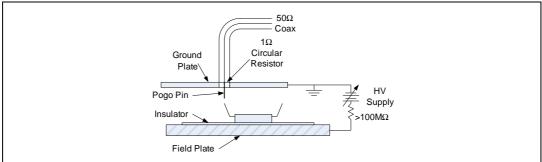

| Figure 153. | ESD test application scheme for HSD placed on a powered module                             | 182 |

| Figure 154. | ESD charge device model test scheme                                                        | 183 |

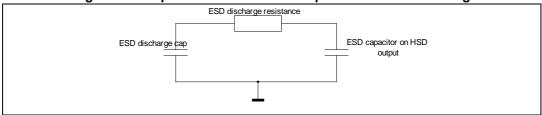

| Figure 155. | Equivalent circuit for ESD protection dimensioning                                         | 184 |

|             | H-Bridge scheme                                                                            |     |

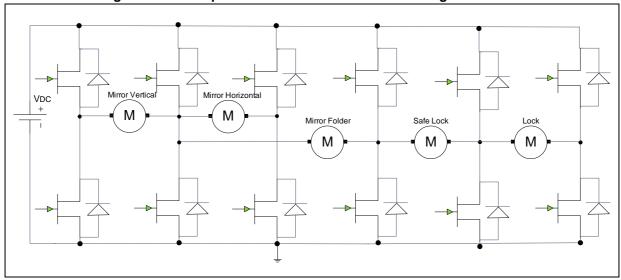

| Figure 157. | Example of automobile multi-motor driving connection                                       | 186 |

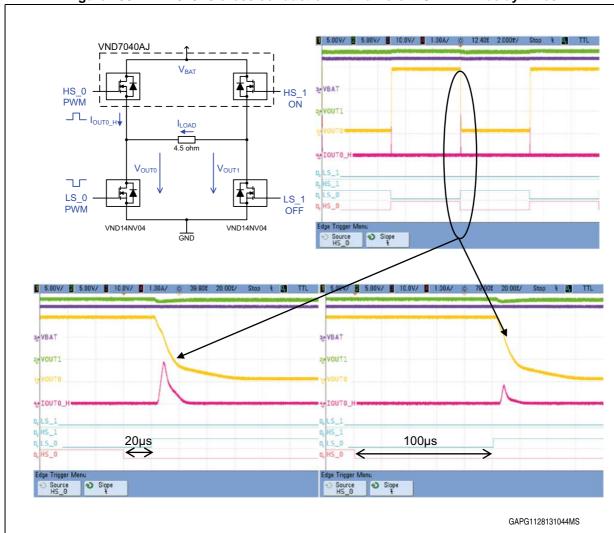

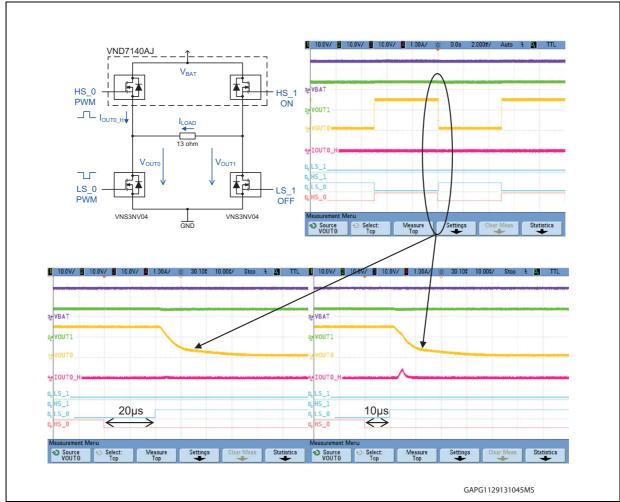

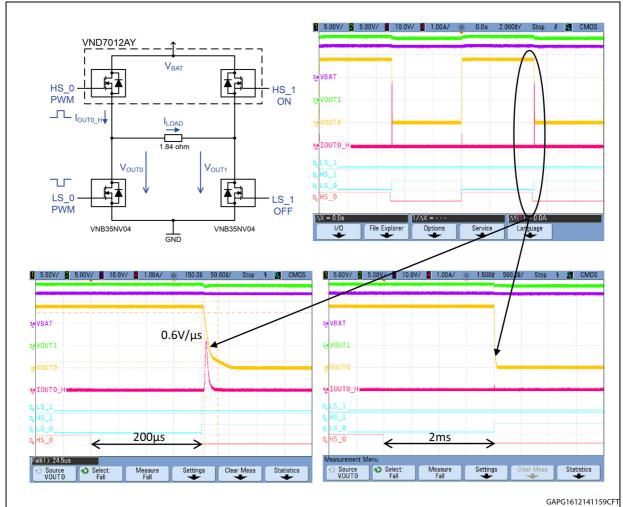

| Figure 158. | VND7040AJ cross conduction with different OMNIFET delay times                              | 187 |

| Figure 159. | VND7140AJ cross conduction with different OMNIFET delay times                              | 188 |

|             | VND7012AY cross conduction with different OMNIFET delay times                              |     |

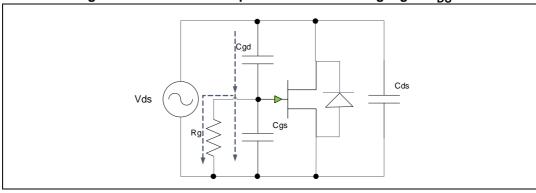

| Figure 161. | PowerMOS capacitance effect during high dVDS/dt                                            | 190 |

| Figure 162. | Test set up for H-Bridge cross current                                                     | 190 |

| Figure 163. | H-Bridge formed by one VND7140AJ and two OMNIFETs II showing the high-side                 |     |

|             | freewheeling phase                                                                         | 192 |

| Figure 164. | H-Bridge formed by one VND7140AJ and two OMNIFETs II showing the high-side                 |     |

|             | freewheeling phase                                                                         | 192 |

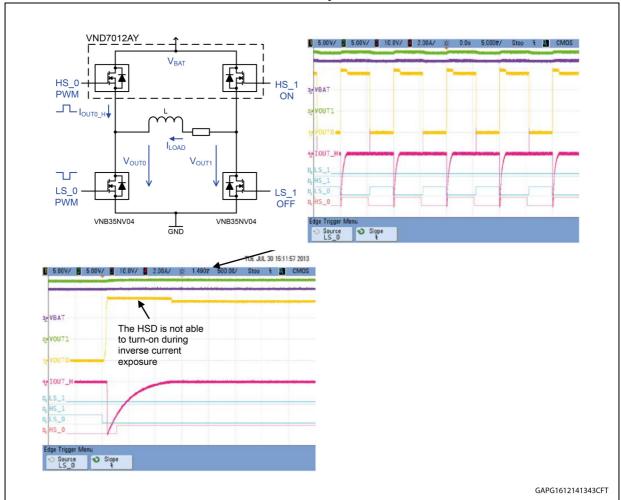

| Figure 165. | H-Bridge formed by one VND7012AY and two OMNIFETs II showing the freewheeling v            | ia  |

|             | HSD body diode                                                                             | 193 |

|             |                                                                                            |     |

UM1922 General items

#### 1 General items

## 1.1 Overview about M0-7 standard high-side drivers

The M0-7 standard high-side drivers are manufactured using STMicroelectronics<sup>®</sup> proprietary VIPower<sup>®</sup> technology. The devices are designed to drive 12 V automotive resistive as well as inductive and capacitive loads connected to ground. A 3.3 V and 5 V CMOS-compatible interface to a microcontroller unit is provided. The products feature a very low quiescent current to preserve battery charge during standby mode. Undervoltage shutdown acts below 4 V in order to ensure the loads are driven when charge pump can deliver sufficient power. Overvoltage clamp structure protects the devices effectively from "ISO 7637-2:2004(E)" pulses (with the exception of load dump pulses, unclamped or clamped above 40 V). At loss of ground the outputs are safely turned-off, current injected into the outputs is less than 2 mA. At loss of V<sub>CC</sub> the outputs are also safely turned-off, but special care must be taken when inductive loads are driven, since additional external protection is required to absorb the demagnetization energy (refer to *Chapter 6: Load compatibility*).

Reverse battery protection is provided in conjunction with external components for monolithic standard high-side drivers, whilst hybrid high-side drivers are reverse battery protected by self turn-on of output channels without the need of external components (refer to *Chapter 2: Reverse battery protection*). Note that no protection features are operating under reverse battery conditions.

M0-7 standard high-side drivers integrate advanced protective functions such as load current limitation, overload active management by power limitation and overtemperature shutdown with configurable latch-off. A FaultRST pin unlatches the output in case of fault or disables the latch-off functionality. A dedicated multifunction multiplexed analog output pin delivers sophisticated diagnostic functions including:

- Proportional load current sense

- Supply voltage feedback

- Chip temperature sense

- Detection of overload

- Short circuit to ground

- Short to V<sub>CC</sub> and

- Off-state open-load

A SenseEnable pin allows off-state diagnosis to be disabled when it is needed to send the module in low power mode. Moreover, thanks to the sense enable functionality, it is possible to share one common external sense resistor among several devices and so to manage a MultiSense diagnostic bus.

General items UM1922

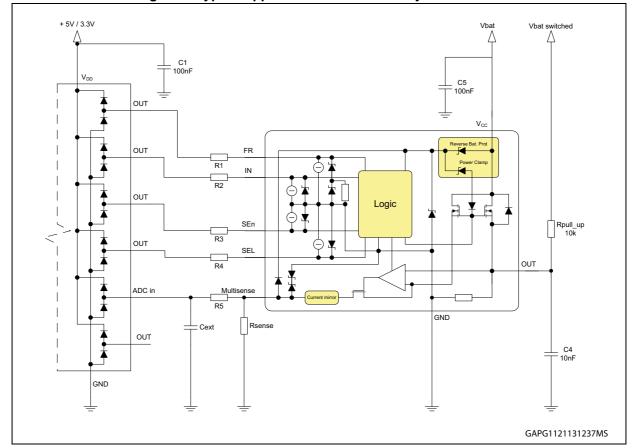

# 1.2 Application schematics – monolithic devices

+ 5V / 3.3V Vbat switched  $V_{DD}$ C5 100nF OUT OUT R1 – 15k IN R2 – 15k OUT Logic SEn Rpull\_up 10k R3 – 15k ОПТ R4 – 15k OUT ADC in R5 – 15k GND Rsense ADC in C4 10nF GND GAPG1121131236MS

Figure 1. Typical application schematics – monolithic devices

UM1922 General items

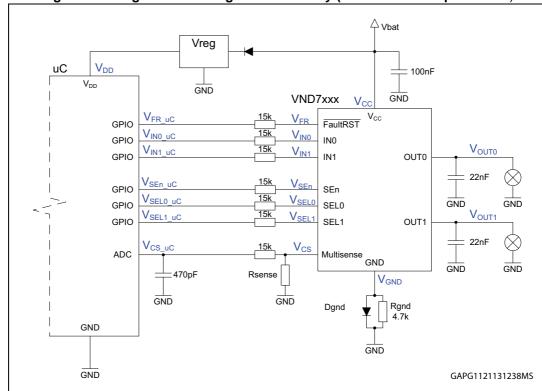

## 1.3 Application schematics – hybrid devices

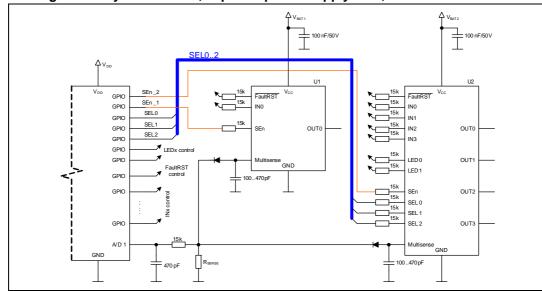

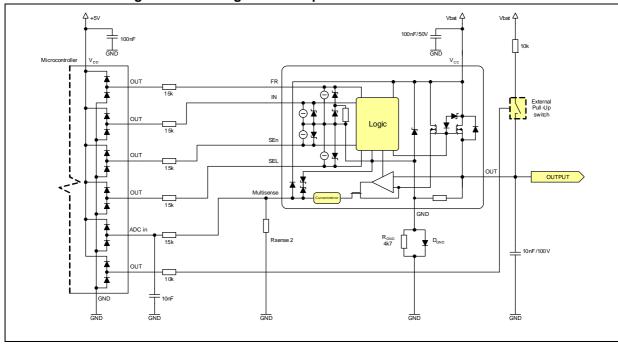

Figure 2. Typical application schematics - hybrid devices

# 1.4 Application schematics – description of external components

- Pull-up: this resistor is optional and is needed when open-load in off state diagnostic is required. It has to be dimensioned to pull up the output above the maximum open-load in off state detection voltage (V<sub>OL</sub> max) and make sure that the output voltage stays below the minimum open-load in off state detection voltage (V<sub>OL</sub> min) in case the load is connected (for details refer to Section 7.2.11: Open load detection in off-state).

- R5//C<sub>EXT</sub>: a low pass-filter, as an RC filter, can be placed across the R<sub>SENSE</sub> resistor to suppress HF noise. The time constant of this filter (τ = RC) should be long enough to effectively suppress the noise and short enough to allow MultiSense signal stabilization taking into account multiplexer delay and settling times. C2 should be placed close to the MCU's A/D input. Also, the ground connection for C2 should be at the same potential as the ground of the A/D reference. The filter resistor R5 is also used to limit the A/D's input pin current (for details refer to Section 7.2.13: MultiSense low pass filtering).

- R6//C<sub>EXT</sub>: this low pass-filter and ADC input connection is optional and is recommended for monolithic devices, when a precise chip temperature or supply

General items UM1922

voltage feedback reading is required. For dimensioning the same recommendations apply as for R5//C2.

- C4: it is recommended to place a ceramic capacitor on each output to dissipate energy of high frequency, high voltage transients, in particular ESD transient pulses. A 100 V ceramic capacitor generally has sufficient voltage capability. The device ESD robustness of each pin is rated in Absolute Maximum Rating chapter of the datasheet (for details refer to *Chapter 11: Usage in "H-Bridge" configurations*).

- C5: C5 capacitor helps to suppress voltage transients that originate from other

actuators connected in parallel and sharing the same battery line. This capacitor will be

capable to suppress only low energetic short transient pulses. The device itself is rated

to sustain ISO 7637-2:2004(E) transient test pulses 1-4 up to test level IV according to

class C. Other methods are needed to protect the module from higher energy

transients, such as load dump.

Moreover C5 capacitor helps to suppress HF noise at the  $V_{CC}$  pin that is generated by the high-side driver device itself. The noise can originate from the charge pump circuitry or from the switching slopes of PWMed outputs.

Using a 100 nF low ESR ceramic capacitor mounted close to device  $V_{CC}$  and GND terminals the devices meet CISPR25 Class 5 requirements measured in conducted emission voltage method in DC, as well as in PWM, operation.

Finally, during a loss of  $V_{CC}$  condition, the C5 capacitor supplies load current for the demagnetization of inductive loads.

- R<sub>SENSE</sub>: R<sub>SENSE</sub> resistor will convert the MultiSense output current, which is a copy proportional to the load current, into a voltage which can be read by the A/D Converter of the Microcontroller. The R<sub>SENSE</sub> should be dimensioned to ensure proper resolution range and granularity to monitor nominal current as well as detecting open load or overload events. Typical values of R<sub>SENSE</sub> are in the range from 1 kΩ to 2.7 kΩ, in order to generate typically 1 V 2 V sense voltage at nominal load current. R<sub>SENSE</sub> selection must also take into account maximum power dissipation and maximum current injection during reverse battery conditions and ISO 7637-2:2004(E) and ISO 7637-2:2011(E) pulse 1 transients. Refer to Section 7.2.6: Considerations on MultiSense resistor choice for current monitorfor details on R<sub>SENSE</sub> dimensioning rules.

- R1-R5: R1-R5 serial resistors are needed on digital inputs in order to limit the current in the input structures as well as in the microcontroller output structures to a safe value during transient and reverse battery conditions. A proper value for such resistors is  $15 \ k\Omega$ .

- No low ohmic impedance paths to GND such as pull down transistors or capacitors shall be connected directly to the digital inputs. In such conditions, device ground shift may trigger intrinsic parasitic structures and an unlimited, destructive current path from  $V_{\rm CC}$  to the digital input will be formed.

- $R_{GND}/D_{GND}$ : a reverse polarity protection network between device ground and module ground is needed for monolithic devices. The diode prevents unlimited destructive current flow through the  $V_{CC}$  GND clamping structure in case of reverse polarity connection.  $R_{GND}$  paralleled to  $D_{GND}$  avoids device ground dropping to negative voltage during turn-off of inductive loads. Typical values range from 1 k $\Omega$  to 4.7 k $\Omega$ , higher values reduce power dissipation under reverse battery condition (for details refer to *Chapter 2: Reverse battery protection*).

Hybrid devices (for classification of Hybrid and Monolithic HSDs please refer to Section 5.1: Classification of M0-7 HSDs) do not need GND network (please refer to Figure 2) in case pulses belonging to ISO 7637-2:2004(E) standard are requested to be passed. A resistive path in the GND connection of Hybrid devices with  $R_{\rm GND} > 300$ ,

57

UM1922 General items

would not properly activate the self-turn on of the Power MOS in case of reverse battery (the load current would circulate into the Body Diode instead). RON in reverse battery conditions with self-turn on is indicated in the Hybrid devices' datasheets. In case ISO 7637-2:2011(E) is requested to be fulfilled the same schematic applies except in case ISO pulses 1 level IV and 2a level IV are requested to be passed. In this case a GND network must be implemented (for details, please refer to Section 3.6.2: Dimensioning of the GND network to pass the ISO n.1 and 2a level IV (2011 edition)).

## 2 Reverse battery protection

#### 2.1 Introduction

A universal problem in automotive environment is the threat of damage when an end user inverts the battery polarity.

Users of battery powered equipment expect safeguards to prevent damage to the internal electronics in the event of reverse battery installation. These safeguards can be either mechanical (use of special connectors) or electronic. In that case battery powered equipment designers and manufacturers must ensure that any reverse current flow and reverse bias voltage is low enough to prevent damage to the equipment's internal electronics. To provide these electronic safeguards, different concepts applying passive or active reverse polarity protection are possible and described in this chapter.

Depending on the type of device (monolithic or hybrid, for classification please refer to Section 5.1: Classification of M0-7 HSDs), a specific protection must be implemented in order not to exceed the device's reverse capability:

- Monolithic HSDs: the reverse battery protection needs to be inserted according to the

instructions suggested in this chapter. In particular, if the reverse polarity protection is

installed on device GND connection, the device will conduct through the body diode of

the power MOSFET with the current limited by the external load. Since no device

intrinsic protection schemes are active in reverse condition, special care must be taken

on total Power Dissipation.

- Hybrid HSDs: in contrast to monolithic devices, all hybrids VIPower HSD do not need any external components to protect the internal logic in case of a reverse battery condition. The protection is provided by internal structure. Moreover, due to the fact that the output MOSFET turns on even in reverse battery mode and thus providing the same low ohmic path as in regular operation condition, no additional power dissipation has to be considered. Even more: if e.g. a diode without any parallel resistor is connected to GND of a hybrid HSD the output MOSFET is unable to turn on and thus the unique feature of the driver is disabled.

## 2.2 Reverse battery protection of monolithic HSDs

Reverse battery protection schemes basically can be grouped in the following categories:

- Active or passive reverse polarity protection

- Reverse polarity protection on supply line (V<sub>CC</sub> terminal) or on GND line (GND terminal)

| Reverse battery protection concept | Chapter | Active/passive | V <sub>CC</sub> terminal/<br>GND terminal | Conduction through output stage |

|------------------------------------|---------|----------------|-------------------------------------------|---------------------------------|

| Schottky Diode                     | 2.2.1   | Passive        | V <sub>CC</sub>                           | No                              |

| Diode    Resistor                  | 2.2.2   | Passive        | GND                                       | Yes                             |

| N-channel MOSEFT                   | 2.2.3   | Active         | GND                                       | Yes                             |

Table 1. Reverse battery protection concepts

16/196 DocID028098 Rev 1

| Reverse battery protection concept | Chapter | Active/passive | V <sub>CC</sub> terminal/<br>GND terminal | Conduction through output stage |

|------------------------------------|---------|----------------|-------------------------------------------|---------------------------------|

| p-channel MOSFET                   | 2.2.4   | Active         | V <sub>CC</sub>                           | No                              |

| Reverse FET                        | 2.2.5   | Active         | V <sub>CC</sub>                           | No                              |

Table 1. Reverse battery protection concepts (continued)

#### 2.2.1 Schottky diode

When the battery is installed backwards, the Schottky diode is reverse—biased and only the rated leakage current  $I_R$  flows. With respect to a standard diode, the Schottky diode has the advantage of a very low voltage drop in forward direction, hence power dissipation is reduced. However, the disadvantage of using a Schottky diode is, that it is typically more expensive than a standard diode.

Below reported, there is the suggested procedure to choose properly the right device. The following parameters will constitute the selection criteria:

- The average current used by the device, electronic module, load to be reverse battery protected. Failure scenarios, such as an output shorted to GND (load short circuit) have to be considered as well.

- The maximum repetitive peak reverses voltage V<sub>RRM</sub>

- The maximum ambient temperature T<sub>amb</sub>

The following inequality must apply in all cases:

$$T_{amb} + R_{th} \cdot P < T_{jMAX}$$

where:

$$P = V_{TO} \cdot I_{F(AV)} + rd \cdot I^2 F(RMS)$$

$I_{F(AV)}$  = maximum average forward current

$I_{F(RMS)} = RMS$  forward current

R<sub>th</sub> = thermal resistance (Junction to ambient) for the device and mounting in use

rd = small signal diode resistance

V<sub>TO</sub> are depending on the special characteristics of the diode.

One important thing to take into account is the peak reverse voltage limit of the Schottky diode:  $V_{RRM} = 100 \text{ V}$  seems a good compromise with respect to the "ISO 7637-2:2004(E)" pulse 1 Test levels IV. In case compliance with "ISO 7637-2:2011(E)" pulse 1 Test level IV is required,  $V_{RRM}$  must be  $\geq 150 \text{ V}$ . The main drawback of this method is the power dissipation in the Schottky diode in forward direction. Depending on the type of package, the  $R_{th}$  and the ambient temperature, the maximum affordable power dissipation in the Schottky diode is typically in the range of 1 W. In consequence the maximum average forward current is limited to the range of 1 A – 2 A.

The direct diode reverse battery protection can also be replaced with a simple fuse. However, upon battery inversion this fuse will blow and the module will need to be replaced or repaired.

#### 2.2.2 Diode + resistor in GND line

The reverse battery protection is applied to the GND terminal of the driver. This kind of protection leaves the output power stage in reverse battery condition conductive through its body diode. The current is limited by the external load. Since no thermal protection works in reverse condition, special attention must be paid to the total power dissipation in the device. During the reverse battery event, the peak junction temperature shall remain safely below the maximum allowed junction temperature ( $T_{TSD\_max}$ ). Considering a voltage drop on the internal body diode of  $V_{F\_max} = 0.7 \text{ V}$ , the resulting power dissipation in the high-side driver per output channel is  $P_D = 0.7 \text{ V} * I_{LOAD}$ .  $Z_{thj-a}$  diagrams reported in HSD datasheets support the user to calculate the maximum affordable load current for a given PCB layout.

Note that the intrinsic diode between MultiSense pin and  $V_{CC}$  pin will be forward biased in reverse battery condition. The current is limited by the external sense resistor. A 1 k $\Omega$  sense resistor will dissipate 250 mW about.

For what concerns the GND path of the device, the integrated V<sub>CC</sub> - GND clamping protection, which circuit behaves like a Zener diode will be forward biased in reverse battery condition. The power dissipation in the GND resistor therefore is determined by  $P_D = (-V_{BAT\ rev} - 0.3\ V)^2 / R_{GND}. \ A\ 1\ k\Omega\ GND\ resistor\ will\ dissipate\ 250\ mW\ about.$

The following figure provides an overview about the resulting voltage levels on pins in a typical application schematic during reverse battery condition.

Figure 3. Voltage levels during reverse battery (diode + resistor protection)

Out = 5 W bulb

Out 0, 1 = 5 W bulb

577

| Pin voltages      | Pin voltages [V] VND7xxxAJ |                      | Pin voltages [V] microcontroller |  |  |

|-------------------|----------------------------|----------------------|----------------------------------|--|--|

| V <sub>CC</sub>   | -16                        | V <sub>DD</sub>      | -0.4                             |  |  |

| V <sub>FR</sub>   | -9.7                       | V <sub>FR_µC</sub>   | -0.7                             |  |  |

| V <sub>INO</sub>  | -10                        | V <sub>IN0_µC</sub>  | -0.7                             |  |  |

| V <sub>IN1</sub>  | -10                        | V <sub>IN1_µC</sub>  | -0.7                             |  |  |

| V <sub>SEn</sub>  | -10                        | V <sub>SEn_µC</sub>  | -0.7                             |  |  |

| V <sub>SEL0</sub> | -10                        | V <sub>SEL0_μC</sub> | -0.7                             |  |  |

| V <sub>SEL1</sub> | -10                        | V <sub>SEL1_μC</sub> | -0.7                             |  |  |

| V <sub>CS</sub>   | -15.3                      | V <sub>CS_µC</sub>   | -0.7                             |  |  |

| V <sub>OUT0</sub> | -15.3                      |                      |                                  |  |  |

| V <sub>OUT1</sub> | -15.3                      |                      |                                  |  |  |

| $V_{GND}$         | -15.4                      |                      |                                  |  |  |

Table 2. Reverse battery-voltages on pins (VND7040AJ)

GND voltage on device is dropping to the reverse battery voltage plus the forward voltage of the integrated  $V_{CC}$  to GND clamping circuit. Voltage on MultiSense pin is dropping to the reverse battery voltage plus the forward voltage across the internal ESD protection diode. The maximum allowed DC output current on MultiSense pin ( $I_{SENSE}$ ) in reverse battery conditions is limited to 20 mA. Therefore the Sense Resistor  $R_{SENSE}$  must be chosen accordingly:

$$R_{SENSE} > (|V_{BAT reverse} - 0.7V|)/0.02A = 765\Omega$$

For generic R<sub>SENSE</sub> dimensioning rules, please refer to *Chapter 7: MultiSense - analogue current sense*.

Due to the clamping voltage of the integrated ESD protection diodes on logic pins (FaultRST,  $IN_x$ ,  $SEL_x$ ,  $SE_n$ ) the voltage on those pins is dropping to -10 V about. Therefore a serial resistor is needed to limit the current and protect the I/O structure on microcontroller port pins and the high-side driver's logic pins.

Furthermore the ground network shall ensure the device will work properly when driving inductive loads and/or is not being damaged when submitted to ISO 7637-2:2011(E) pulse 1 test level IV pulses.

The diode at the GND terminal blocks the current through the forward biased internal substrate diode of the HSD during reverse battery condition.

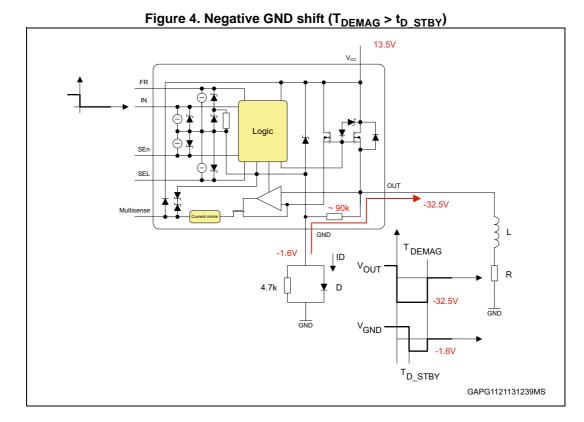

A resistor connected in parallel to the diode is recommended in case the device drives a high inductive load with a demagnetization time longer than  $t_{D\_STBY}$  (delay time for the device to reach standby mode after the last logic pin (IN<sub>x</sub>, FaultRST, SE<sub>n</sub> and SEL<sub>x</sub>) is set low). The purpose of this resistor is to suppress a negative voltage on the GND pin during the standby mode if the demagnetization phase is still ongoing. Without this resistor, the low supply current in standby mode (I<sub>soff</sub> = 0.5  $\mu$ A max at 85 °C) allows the GND pin to be pulled negative by the demagnetization voltage on the output (~ (V<sub>CC</sub> - V<sub>CLAMP</sub>) ~ (13.5 V – 46 V) = -32.5 V) via an internal pull-down resistor (~90 k $\Omega$ ) on the output (see *Figure 4*). If the negative ground shift exceeds the input high level threshold, the device leaves the standby mode and tends to turn on. The GND pin is immediately pulled high

(~ 600 mV) by the increased supply current I<sub>SON</sub> so that the standby mode will be activated again after  $t_{D\_STBY}$ . As a result, we could see short negative peaks on the GND pin with period of  $t_{D\_STBY}$  during the whole demagnetization phase. These peaks are not long enough to activate the HSD output, which means the device works safely even without the GND resistor. However, this resistor is still needed in order to suppress the described parasitic oscillations (if  $T_{DEMAG} > t_{D\_STBY}$ ).

The ground network can be safely shared amongst several different high-side drivers, provided they are supplied from the same supply rail. Sharing the ground network is even possible among different HSDs, when they are supplied from different supply rails. In this case however, special precautionary measures must be applied (for details refer to Section 8.3: Paralleling of GND protection network). The presence of the ground network will produce a shift (~ 600 mV) in the input threshold. This shift will not vary, if more than one HSD share the same diode/resistor. The diode at the GND terminal allows the high-side driver to clamp positive ISO pulses above 46 V (the typical clamping voltage of the HSD). Negative ISO pulses still pass GND and logic terminals. The diode should withstand clamped ISO currents in case of positive ISO pulses and reverse voltages in case of negative ISO pulses.

#### **Dimensioning of the GND diode**

The most severe positive "ISO 7637-2:2004(E)" pulse we have to consider is test pulse 2a at level IV (50 V during 50  $\mu$ s). This voltage is considered on top of the nominal supply voltage of 13.5 V – so the total voltage is 63.5 V. The M0-7 HSDs have a clamping voltage  $V_{CLAMP} = 46$  V typical. In case of a typical device the remaining voltage is 63.5 V - 46 V - 0.7 V = 16.8 V. The ISO pulse generator output impedance is 2  $\Omega$ . With this the resulting peak current through the diode is 8.4 A for duration of 50  $\mu$ s.

The most severe negative "ISO 7637-2:2004(E)" pulse we have to consider is test pulse 1 at level IV (-100 V at 1 ms). This pulse is directly transferred to the GND pin via the internal clamping. So, the maximum peak reverse voltage of the diode should be at least 100 V. In case "ISO 7637-2:2011(E)" pulse 1 test level IV compliance is required, the maximum peak reverse voltage of the diode should be at least 150 V.

Note: The Diode will work in avalanche mode if the pulse level is above the rated reverse voltage.

#### Conclusion:

Note:

The dimensioning the GND diode must fulfill the following:

Maximum peak forward current: 8.4 A for 50 µs for ISO 7637-2:2004(E)

Maximum reverse voltage: -100 V for ISO 7637-2:2004(E) resp. -150 V

for ISO 7637-2:2011(E)

As seen from above explanation, the HSD with a diode protection at the GND pin doesn't clamp negative ISO pulses on the supply line. Therefore an appropriate serial protection resistor should be used between microcontroller and HSD (typically 15 k $\Omega$ ). The resistor value should be calculated according to the maximum injected current to I/O pin of the used microcontroller and to the maximum Input sink current of the HSD.

Diode parameters can be lower if an external clamping circuitry is used (e.g. HSD module is supplied from a protected power supply line).

57

20/196 DocID028098 Rev 1

#### **Dimensioning of the GND resistor**

The GND resistor is recommended in case of a high inductive load. To determine if the resistor is needed or not, we need to know the demagnetization time ( $T_{DEMAG}$ ). The resistor is recommended if  $T_{DEMAG}$  is higher than the standby delay time ( $t_{D-STBY}$ ).

A typical  $t_{\text{D STBY}}$  value of 350  $\mu s$  is considered in this comparison.

$T_{DEMAG}$  can be determined by either measurement (*Figure 6*,  $R_{GND}$  = 4.7 k $\Omega$ , Load: Relay 270 mH/ 90  $\Omega$  alternatively Bulb on a typical wire harness with 6  $\mu$ H stray inductance) or calculation, using *Equation 1* and *Equation 2*.

#### **Equation 1**

$$V_{DEMAG} = V_{BAT} - V_{CLAMP}$$

#### **Equation 2**

$$T_{DEMAG} = \frac{L}{R} \cdot ln \left( \frac{|V_{DEMAG}| + I_0 \cdot R}{|V_{DEMAG}|} \right)$$

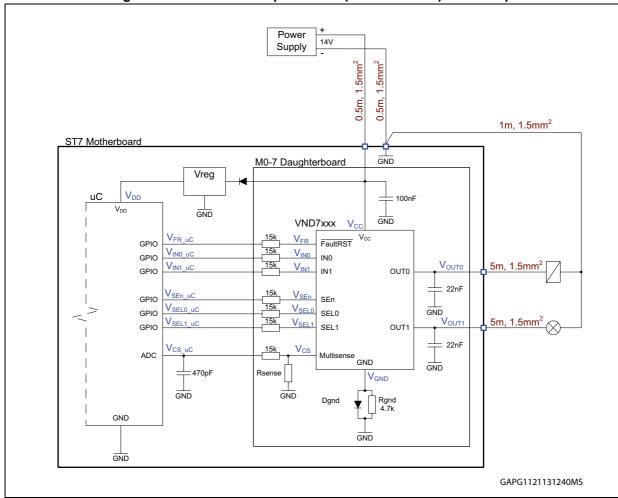

Figure 5. GND resistor requirements (inductive load)-test setup

22/196

Figure 7. Measurement example ( $t_{DEMAG} > t_{D-STBY}$ ) with 4.7 k $\Omega$  GND resistor

The experimental trials have shown:

- The operation with high inductivity load (T<sub>DEMAG</sub> > t<sub>D\_STBY</sub>) is correct even without the GND resistor (only the diode), knowing that the device GND pin oscillation with period of t<sub>D\_STBY</sub> may be present (see *Figure 6*)

- In all cases, the 10  $k\Omega$  resistor was enough to reduce the GND shift below the logic input activation level (so eliminate the oscillations)

- The 4.7 k $\Omega$  appears to be the best compromise between the GND shift safety and power dissipation during static reverse battery condition (~50 mW)

The value of the resistor should be low enough to be sure that the negative voltage at the GND pin is suppressed as much as necessary to keep the device off. This means the  $V_{GND}$  should be kept above -1.3 V.

The minimum resistor value is determined by the maximum DC reverse ground pin current of the HSD in reverse battery condition:

$$R_{GND} \ge \frac{V_{BAT(reverse)}}{I_{GND(reverse)max}} = \frac{16V}{200mA} = 80\Omega$$

In order to keep the power dissipation on the resistor during reverse battery condition as low as possible, it is recommended to select the resistor value close to the maximum value (4.7 k).

#### Summary - dimensioning of the resistor

Resistor recommended if:  $T_{DEMAG} > t_{D\_STBY}$ Resistance: 4.7 k $\Omega$  (or lower)

Voltage capability: min. 150 V (ISO 7637:2-2011(E) pulse 1 at level IV)

min. 100 V (ISO 7637:2-2004(E) pulse 1 at level IV)

Power dissipation (reverse battery): min. 50 mW (4.7 kΩ)

Example with relay coil:

In case of a relay coil connected supposing following conditions:

Load resistance:  $R_{LOAD} = 90 \Omega$  Wiring inductances: L = 270 mH Initial current  $I_0$ : 0.14 A

Applying Equation 2, yields a T<sub>DEMAG</sub> = 1.0 ms > t<sub>D\_STBY</sub>

Example with resistive load with long wire harness:

In case of a resistive load connected via long wires, supposing following conditions:

Load resistance:  $R_{LOAD} = 5 \Omega$

Wiring inductances:  $L = 5\mu H$  (in case of very long cabling)

Initial current  $I_0$ : 2.7 A

Applying Equation 2, yields a  $T_{DEMAG} = 0.4 \mu s \ll t_{D STBY min}$

Example with short circuit with long wire harness:

In case of a resistive load connected via long wires, supposing following conditions:

Load resistance:  $R_{LOAD} = 100 \Omega$

Wiring inductances:  $L = 5 \mu H$  (in case of very long cabling)

Initial current I<sub>0</sub>: 130 A (I<sub>LIMH max</sub> - lowest ohmic monolithic HSD

VN7010AJ)

Applying Equation 2, yields a  $T_{DEMAG} = 18\mu s \ll t_{D\_STBY\_min}$

This demagnetization phase lasts very short time in comparison to the standby delay time so, in case of not highly inductive loads, no GND resistor is needed in parallel to the GND diode.

#### 2.2.3 N-channel MOSFET in GND line

In comparison to the solutions described in the previous chapters, reverse polarity protection with MOSFETs offer two main advantages: lower power losses and minimal voltage drop. Generally the MOSFET's body diode is oriented in the direction of normal current flow. When the battery is installed incorrectly, the N-MOS (P-MOS) FET's gate voltage is low (high), preventing it from turning ON.

When the battery is properly installed and the portable equipment is powered, the N-MOS (P-MOS) FET's gate voltage is taken high (low) and its channel shorts out the diode.

DocID028098 Rev 1

A voltage drop of  $R_{DS(on)} \times I_{SON}$  is seen in the ground return path when using the N-MOS FET. A voltage drop of  $R_{DS(on)} \times I_{LOAD}$  is seen in the power path when using the PMOS FET. In the past, the primary disadvantage of these circuits has been the high cost of low  $R_{DS(on)}$ , low-threshold voltage FETs. However, advances in semiconductor processing have resulted in FETs that provide minimal drops in small packages.

The N-channel MOSFET is connected in such a way, that its gate is driven directly by the battery voltage and its drain is connected to ground. In normal condition it is ON whilst a reverse battery event switches it OFF (because  $V_{GS} \le 0$ ) and protects the HSD.

In *Figure 8* is reported a generic schematic with N-channel MOSFET configuration. In this case, like for the solution with Diode || Resistor network in the GND line, the HSD's output stage body diode is forward biased and therefore is conducting during the reverse battery. The current is limited by the external load. Since no thermal protection works in reverse condition, special care must be taken on the total power dissipation in the device. During the reverse battery event, the peak junction temperature shall remain safely below the maximum allowed junction temperature ( $T_{TSD_max}$ ). Considering a voltage drop on the internal body diode of  $V_{F_max} = 0.7 \text{ V}$ , the resulting power dissipation in the HSD per output channel is  $P_D = 0.7 \text{ V} \cdot I_{LOAD}$ .

Z<sub>thj-a</sub> diagrams reported in HSD datasheets help the user to calculate the maximum affordable load current for a given PCB layout.

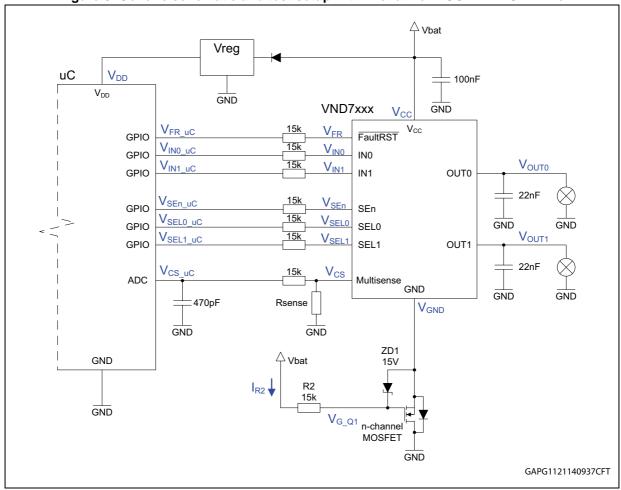

Figure 8. Generic schematic and test setup with N-channel MOSFET in GND line

Measured values (VND7020AJ)

Table 3. Static reverse battery - voltages on pins

|                       | Reverse battery (V <sub>CC</sub> = -16 V) | Normal operation (standby mode) | Normal operation<br>(out0=on, out1 = off) | Normal operation<br>(out0=on, out1 = on) |

|-----------------------|-------------------------------------------|---------------------------------|-------------------------------------------|------------------------------------------|

| V <sub>CC</sub> [V]   | -15.99                                    | 14                              | 13.97                                     | 13.95                                    |

| V <sub>GND</sub> [V]  | -15.37                                    | 0                               | 0.000028                                  | 0.000042                                 |

| V <sub>G_Q1</sub> [V] | -15.92                                    | 13.97                           | 13.95                                     | 13.94                                    |

| Ι <sub>R2</sub> [μΑ]  | -4.1                                      | 0.2                             | 0.2                                       | 0.2                                      |

Table 3 reports the measurement results on VND7020AJ test vehicle: GND voltage on device is dropping to the reverse battery voltage plus the forward voltage of the integrated  $V_{CC}$  to GND clamping circuit (substrate diode). Voltage on MultiSense pin is dropping to the reverse battery voltage plus the forward voltage across the internal ESD protection diode. The maximum allowed DC output current on MultiSense pin ( $I_{SENSE}$ ) in reverse battery conditions is limited to 20 mA. Therefore the sense resistor  $R_{SENSE}$  must be chosen accordingly:

26/196 DocID028098 Rev 1

$R_{SENSE} > (|V_{BAT}|_{reverse} - 0.7 \text{ V}|) / 0.02 \text{ A} = 765 \Omega$

For generic R<sub>SENSE</sub> dimensioning rules, please refer to *Chapter 7: MultiSense - analogue*

Due to the clamping voltage of the integrated ESD protection diodes on logic pins (FaultRST, IN<sub>x</sub>, SEL<sub>x</sub>, SE<sub>n</sub>) the voltage on those pins is dropping to -10 V about. Therefore a serial resistor is needed to limit the current and protect the I/O structure on microcontroller port pins and the high-side driver's logic pins. The gate voltage of the N-channel MOSFET is pulled down to the reverse battery voltage, ensuring the MOSFET is fully off. In normal operation only the leakage current of ZD1 Zener diode is flowing through R2 to GND. In order to minimize this current even at higher supply voltages, a diode with higher Zener voltage (i.e. 18 V) might be chosen. The Zener voltage should be anyway always lower than the maximum rated Gate Source Voltage V<sub>GS</sub> of the N-channel MOSFET.

The resistor R2 limits the current through the Zener diode at supply voltages higher than the Zener voltage and limits the charging/discharging current of the gate. In addition the resistor R2 together with the gate capacitance of the N-channel MOSFET determines the turn-off time when exposed to fast negative transients or abrupt reverse polarity according to the LV 124: 2009-10 standard. 15 k $\Omega$  as demonstrated by the experiment reported below appears to be a good compromise between minimizing the charging/discharging current and ensuring a fast turn-off time.